## DDR4-3200 Channel Modeling and Signal Integrity Analysis Using an FPGA

Presented by Benjamin Dannan October 20, 2020 Technical Session

## **Presenter Bio**

Benjamin Dannan has a multi-faceted background that includes a wide range of professional engineering and military experiences. He is a specialist in signal and power integrity concepts, high-speed circuit and multi-layered PCB design, vision systems, robotics, as well as has multiple years of experience with EMC product development and certifications to support global product launches. Benjamin graduated from Purdue University with a BSEE, and from Penn State University with his Masters of Engineering in Electrical Engineering. He also holds a certification in cybersecurity. In addition to being a recent DesignCon 2020 Best Paper Award winner, he is also an IEEE senior member.

http://www.linkedin.com/in/benjamin-dannan

## Outline

- Objectives & Background

- Simulation Platform

- DDR4 Interface Background

- UDIMM Channel Model Analysis

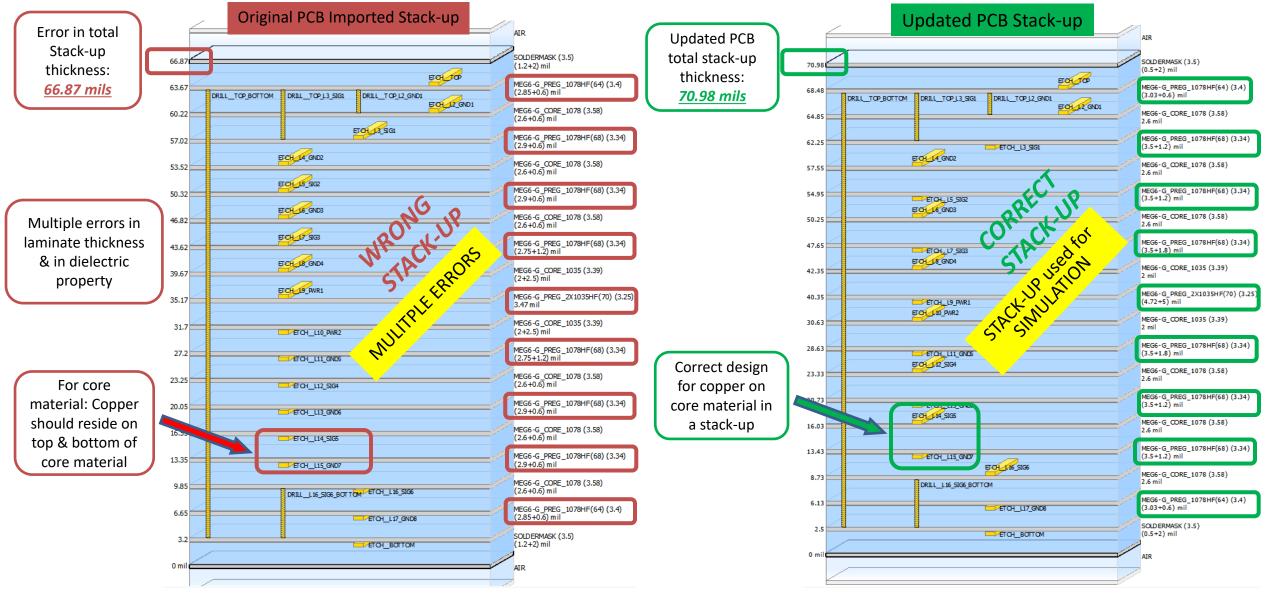

- VCK190 PCB Stack-up Analysis

- VCK190 Channel Model Analysis

- Channel Model Setup

- Channel Simulation Initial Results

- Channel Simulation Post-Tuning Results

- Conclusions

Source: dilbert.com

## **Today's Objectives**

- ✓ Understand how to setup DDR4 model

- ✓ Simulate a DDR4 Model

- ✓ Analyze the results

- 2. Import Layout file into ADS

- 3. Verify PCB stack-up, substrate material and properties

- 4. Use SIPro simulate DDR4 channel model(s)

- 5. Build DDR4 Channel Model in Memory Designer

- 6. Simulate Model

- 7. Analyze Results Tune Channel and Re-simulate

## Background

- 400 hours of video are uploaded to YouTube every minute [1]

- 1,000,000,000+ hours of videos are watched on YouTube everyday [1]

- 350 million photos are uploaded to Facebook daily, with 14.5 million photo uploads per hour [2]

- Al is quickly becoming part of everyday life

$\circ$  Experts state that ML will require 6X amount of DDR than standard cloud server [3].

There is a need to store data and process it quickly

Making memory and fast-storage solutions central to the basic function of computing.

## Background

#### Why do you care about Signal Integrity on DDR4?

"There is no Black or White for high speed digital signals! Just different levels of grey. It is important to know where a design is located on this grey scale."

- Hermann Ruckerbauer (EyeKnowHow)

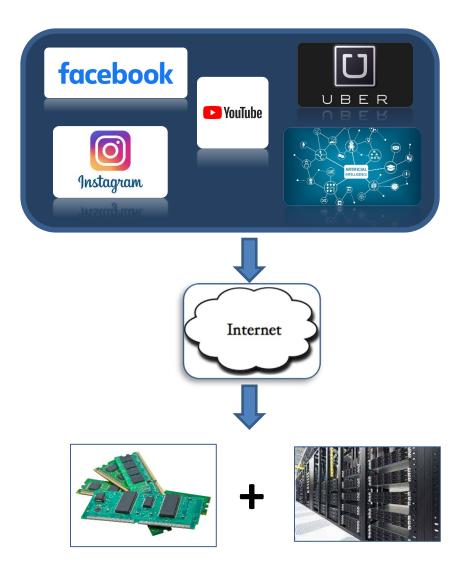

- DDR4-3200 has reduced margin vs. DDR3 => SI and PI become more critical for designs

- SHRINKING Unit Interval (UI) DDR4-3200 (3200 MT/s) UI = 312.5 ps

- SK Hynix unveiled the world's <u>first</u> 64 GB DDR5-4800 and DDR5-5600 DIMMs [3]

- DDR5 UI is much smaller!

- DDR5-4800 UI = 208.3 ps and DDR5-5600 UI = 178.571 ps

- DDRx Data valid window & insertion loss targets continue to shrink

- Memory bottleneck is coming!

Source: Onsemi.com

## **Simulation Platform**

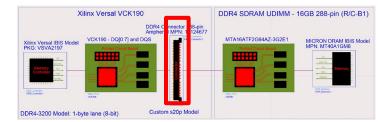

## VCK190 Evaluation Kit with Versal FPGA

- Multiple high-speed digital interfaces (PCIe G4, DDR4, LPDDR4, HDMI)

- Versal FPGA memory controller has many features:

- DDR4, DDR4 3DS, LPDDR4/4X support

- Multi-Rank and Dual-slot configuration support

- 1<sup>st</sup> FPGA with an integrated DDR4-3200 memory controller

- UDIMM interface

- DDR4 DIMM 288 position connector Amphenol MPN: 10124677 [7]

- Simulation Models will use Micron MTA16ATF2G64AZ-3G2E1 (R/C B1) UDIMM

- VCK190 Includes Micron UDIMM MPN: MTA9ADF1G72AZ-3G2E1 (R/C ZZ) desired model unavailable, EBD model available

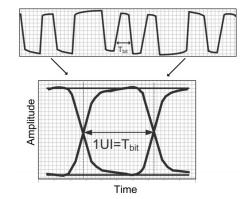

## **DDR4 Interface Background (basics)**

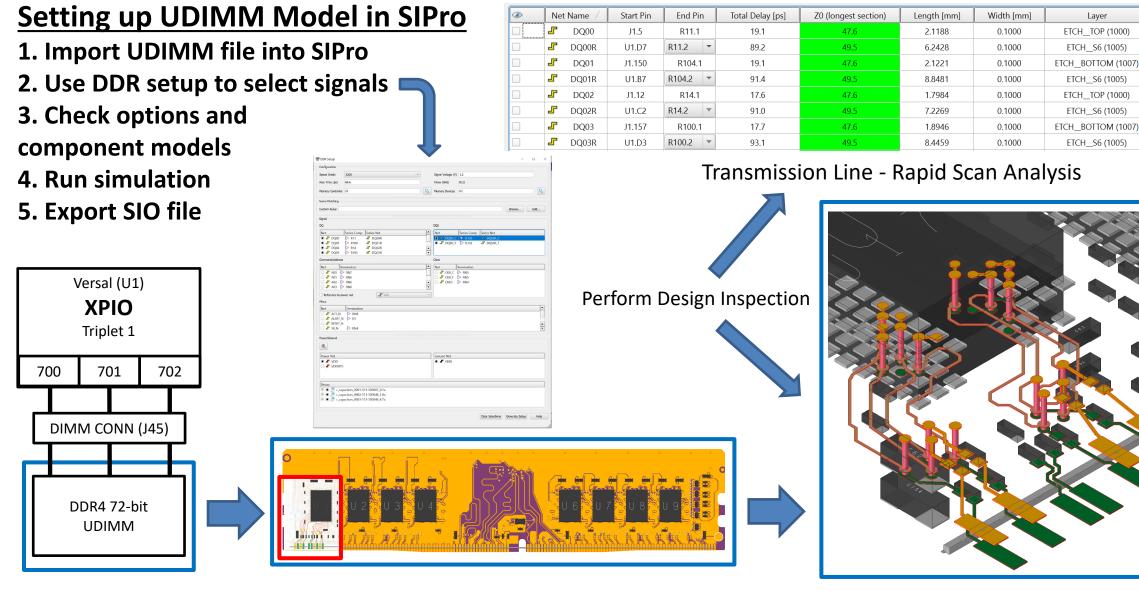

# UDIMM (R/C B1) DDR4 Channel Model

Layer

Via Count

## VCK190 18L PCB Stack-up Analysis

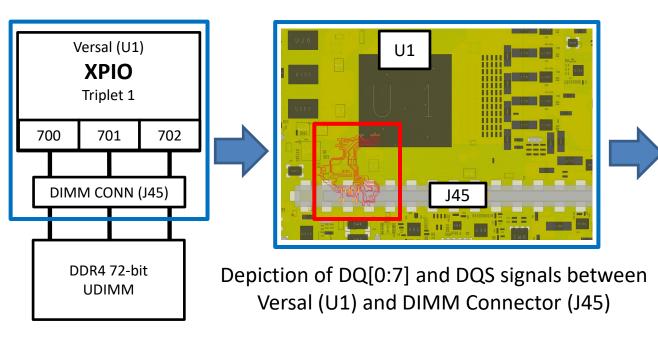

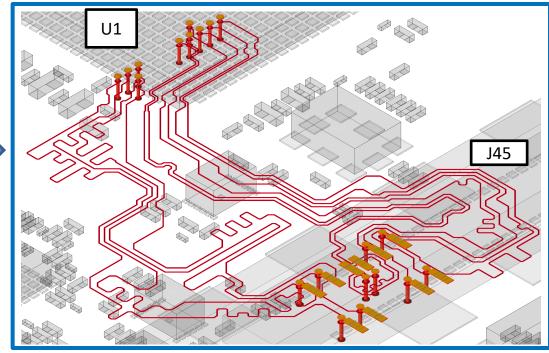

## VCK190 DDR4 Channel Model

#### Setting up VCK190 Model in SIP

- 1. Import VCK190 board file into SIP

- 2. Use DDR setup to select signals

- 3. Check options and

#### component models

- 4. Run simulation

- **5. Export SIO file**

| lodel in SiPro  | Ø ∇    | Net Name          | Start Pin | End Pin | Total Delay [ps] | Z0 (longest section) | Length [mil] | Width [mil] | Width2 [mil] | Spacing [mil] | Layer               | Via Count |

|-----------------|--------|-------------------|-----------|---------|------------------|----------------------|--------------|-------------|--------------|---------------|---------------------|-----------|

|                 | Filter | Filter            | Filter    | Filter  | Filter           | Filter               | Filter       | Filter      | Filter       | Filter        | Filter              | Filter    |

| file into SIPro |        | DDR4_DIMM1_DQ0    | U1.BE41   | J45.5   | 443.1            | 45.4                 | 2669.1       | 3.3         |              |               | ETCH_L5_SIG2 (1004) | 2         |

|                 |        | DDR4_DIMM1_DQ1    | U1.BF41   | J45.150 | 441.6            | 45.4                 | 2660.3       | 3.3         |              |               | ETCH_L5_SIG2 (1004) | 2         |

| ct signals      |        | DDR4_DIMM1_DQ2    | U1.AV41   | J45.12  | 442.9            | 45.4                 | 2668.0       | 3.3         |              |               | ETCH_L5_SIG2 (1004) | 2         |

|                 |        | DDR4_DIMM1_DQ3    | U1.AU41   | J45.157 | 443.0            | 45.4                 | 2660.3       | 3.3         |              |               | ETCH_L5_SIG2 (1004) | 2         |

|                 |        | DDR4_DIMM1_DQ4    | U1.BG41   | J45.3   | 437.0            | 45.4                 | 2630.9       | 3.3         |              |               | ETCH_L5_SIG2 (1004) | 2         |

|                 |        | DDR4_DIMM1_DQ5    | U1.BF42   | J45.148 | 432.0            | 45.4                 | 2599.0       | 3.3         |              |               | ETCH_L5_SIG2 (1004) | 2         |

|                 |        | DDR4_DIMM1_DQ6    | U1.AW41   | J45.10  | 435.5            | 45.4                 | 2621.2       | 3.2         |              |               | ETCH_L5_SIG2 (1004) | 2         |

|                 |        | DDR4_DIMM1_DQ7    | U1.AW40   | J45.155 | 427.8            | 45.4                 | 2572.1       | 3.2         |              |               | ETCH_L5_SIG2 (1004) | 2         |

| Perform Design  |        | DDR4_DIMM1_DQS0_C | U1.BA41   | J45.152 | 449.5            | 45.7                 | 2716.0       | 3.2         |              |               | ETCHL5_SIG2 (1004)  | 2         |

|                 |        | DDR4_DIMM1_DQS0_T | U1.AY41   | J45.153 | 450.5            | 45.7                 | 2722.6       | 3.2         |              |               | ETCH_L5_SIG2 (1004) | 2         |

| Inspection      |        |                   |           |         | Trans            | smission Lir         | ne - Rapi    | id Scan     | Analysis     |               |                     |           |

#### Transmission Line - Rapid Scan Analysis

#### EDI CON

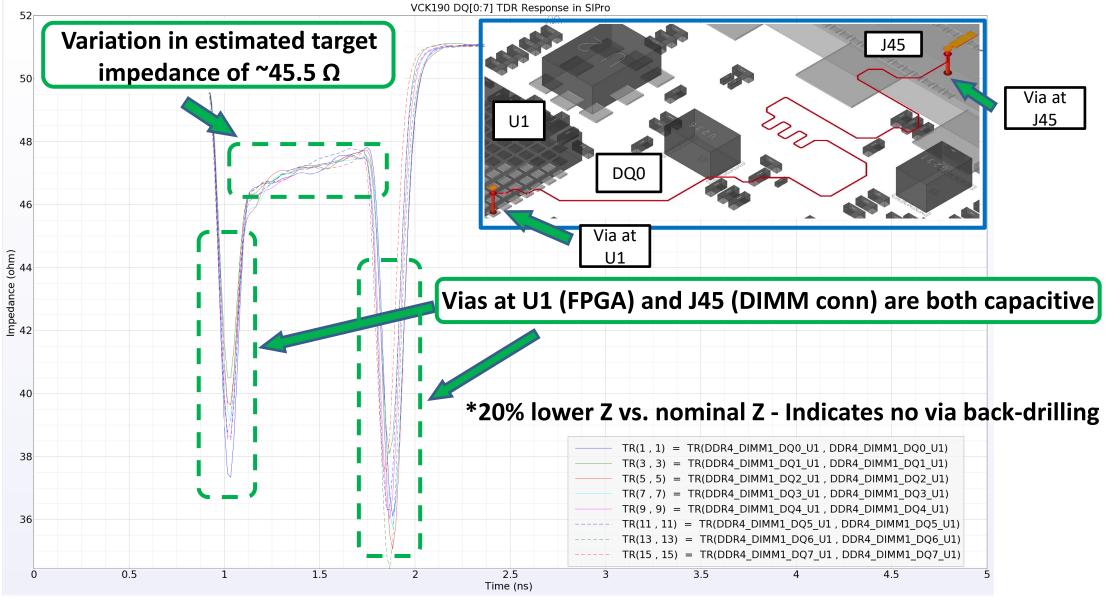

# VCK190 DQ[0:7] Channel Model Impedance

Let's do a quick check of impedance for DQ signals on Layer 5 to determine the target impedance......

| + <b>#</b> +                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | Analyze                               | Optimize                  |         | • O Statistical |            |       |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------|---------------------------|---------|-----------------|------------|-------|

| •                             | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ۱. | Variables                             |                           |         |                 |            | Reset |

|                               | 10      Pr_4_4/00        10      Statute        10      Pr_4_4/00        10      Pr_4_4/00        11      Pr_4_4/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | Name                                  | Nominal                   |         |                 |            | ^     |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | freq                                  | 2 GHz                     |         |                 |            |       |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | Length                                | 500 mil                   |         |                 |            |       |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | Width                                 | 3.3 mil                   |         |                 |            | ~     |

|                               | PP2_UL_URA        PP |    | Show: 🗹 Li<br>Electrical<br>TML Prope |                           | Substra | nte Vars 🗌 Mata | erial Vars |       |

| Substrate                     | 128-05005-01-B01-V06_lib:tech                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |                                       |                           |         | Real            | Imag       | ^     |

| Type Stripline Single-Ended ~ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | Zc (ohm) 45.6685                      |                           |         | -0.57006        |            |       |

| Top plane                     | ETCH_L4_GND2 ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | Gamma (1/m)                           |                           |         | 1.14439         | 79.0065    |       |

| Signal ETCH_L5_SIG2 ~         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | Attenuation (dB/mil)                  |                           |         | 0.000252478     | 0          |       |

| Bottom plane                  | Bottom plane ETCH_L6_GND3 ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |                                       | Attenuation (dB) 0.126239 |         |                 | 0          |       |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | Delay (ns/mil) 0.000159693            |                           | 0       |                 |            |       |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | Delay (ns)                            |                           |         | 0.0798466       | 0          | ~     |

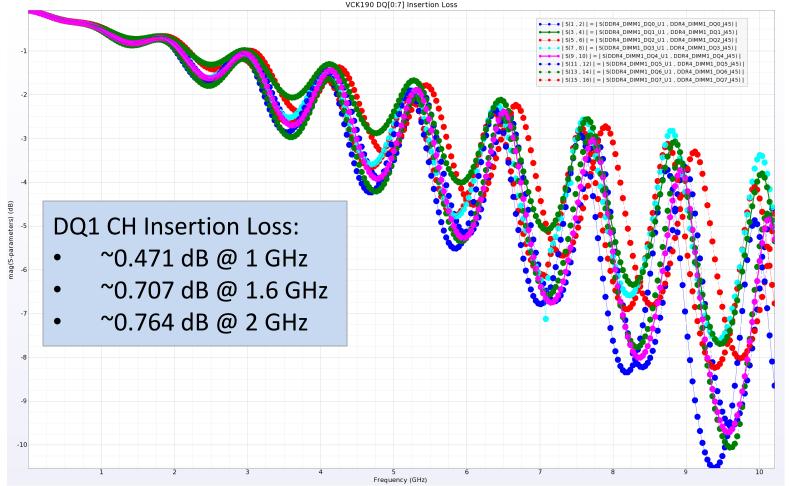

# VCK190 DQ[0:7] Channel Insertion Loss Results

$atten [dB/inch] \approx \frac{31.6}{(W[mils] + T[mils]) * Z_0} \sqrt{f[GHz]} + 2.32 \times f[GHz] \times Df \times \sqrt{Dk}$ [11]

Where for MEG6 R-5670(G) Prepreg 1078, 68% resin content:

- W = Width = 3.3 mils

- T = Trace thickness (inches) = 0.5 oz CU = 0.6 mil

- Material's dissipation factor (Df)= 0.002 @ 2 GHz

- Dielectic constant (Dk) = 3.34 @ 2 GHz

- DQ0\_Len = 2.6603 inch

- Z<sub>0</sub> = 45.6 Ω

$\begin{array}{l} atten_{DQ1\_2.6603\_in} \approx 0.497 \ dB \ @ \ 1.0 \ GHz \\ atten_{DQ1\_2.6603\_in} \approx 0.629 \ dB \ @ \ 1.6 \ GHz \\ atten_{DQ1\_2.6603\_in} \approx 0.703 \ dB \ @ \ 2.0 \ GHz \end{array}$

=> Good correlation!

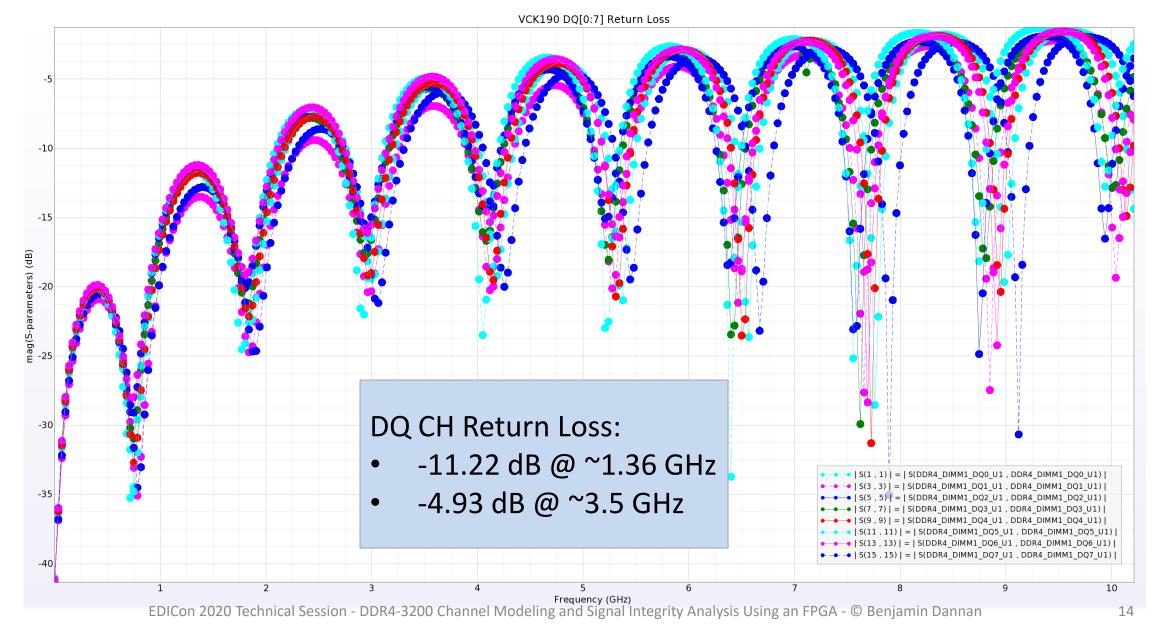

## VCK190 DQ[0:7] Channel Return Loss Results

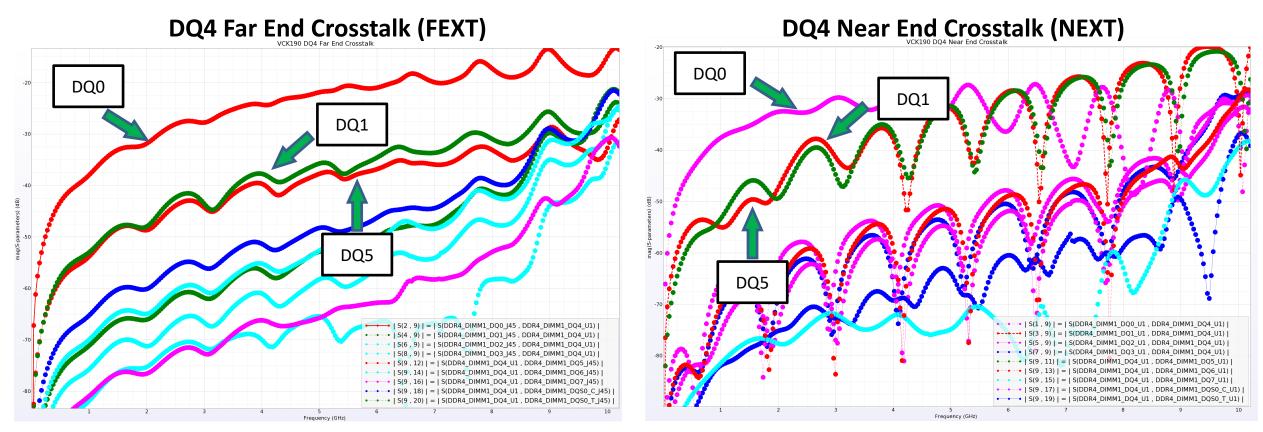

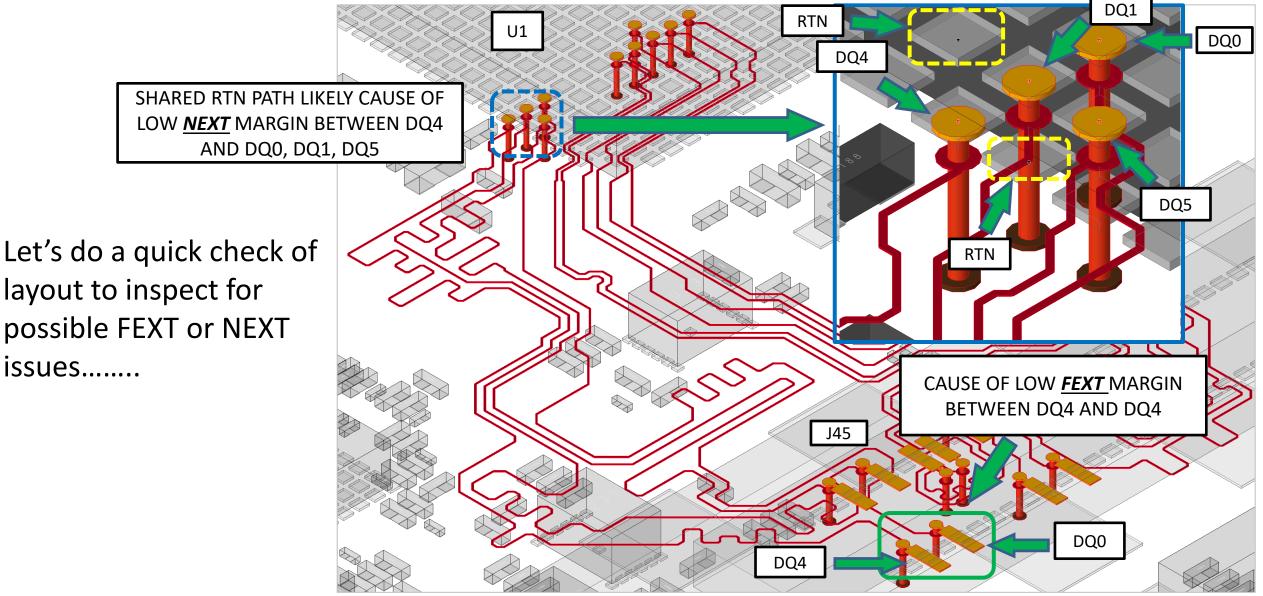

# **CON** VCK190 DQ4 Channel Far End and Near End Crosstalks Results

Significant eye closure due to crosstalk must be accounted for in system analysis

- DQ4 has ~10 dB less margin to DQ0 in both in FEXT and NEXT at 1.6 GHz

- DQ1 and DQ5 in both the FEXT and NEXT have the second least margin to DQ4

# VCK190 DQ4 Channel Far End and Near End Crosstalks Results

# VCK190 DQ[0:7] Channel Impedance Analysis

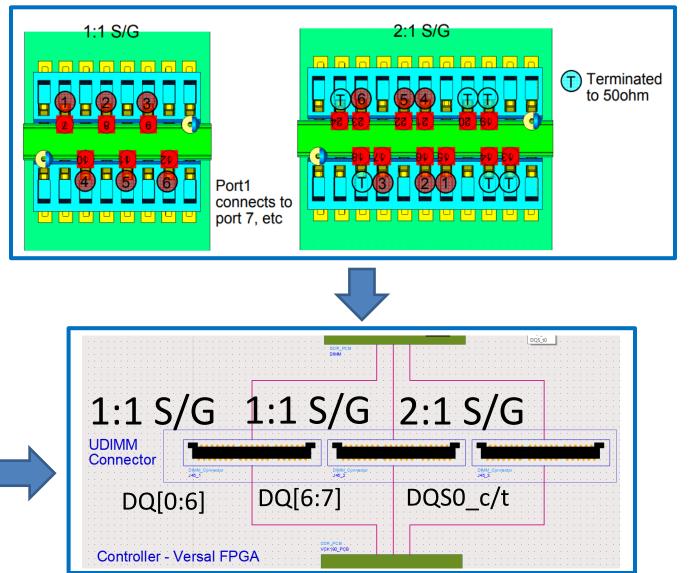

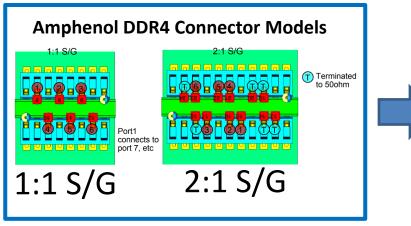

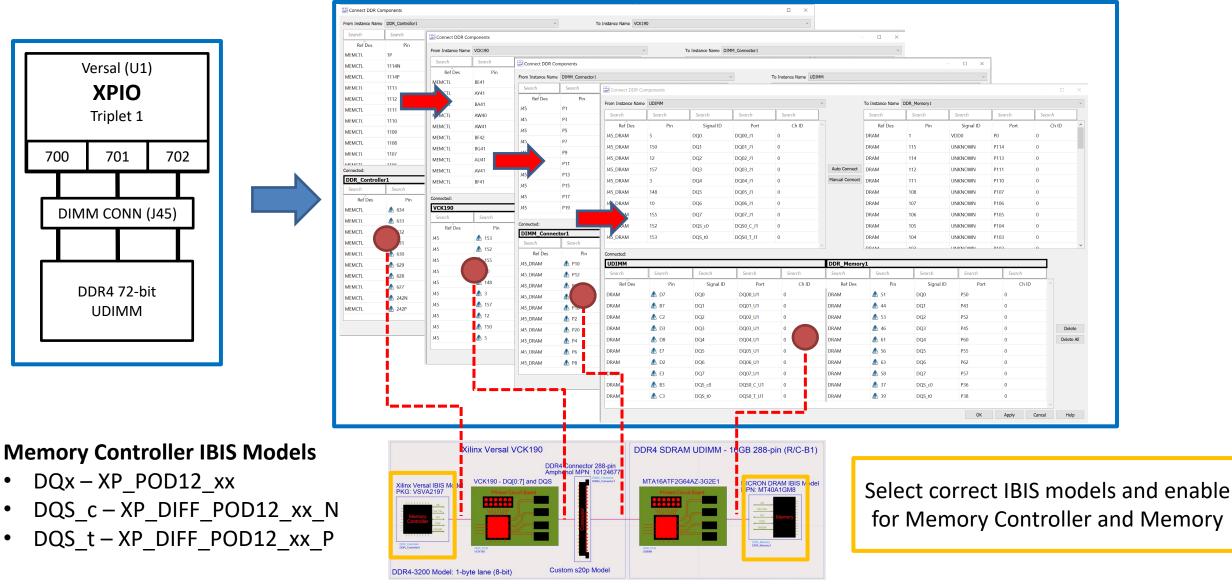

## **DIMM Connector Channel Model Setup**

To simulate complete DDR4 byte lane:

- Only 6 through ports available on 1:1

S/G model

- => 2 instances used for DQ[0:7]

- 2:1 S/G model used for Differential pairs (DQS0\_t/DQS0\_c)

For the connector model in Memory Designer.....

Is this the best way to setup the connector model?

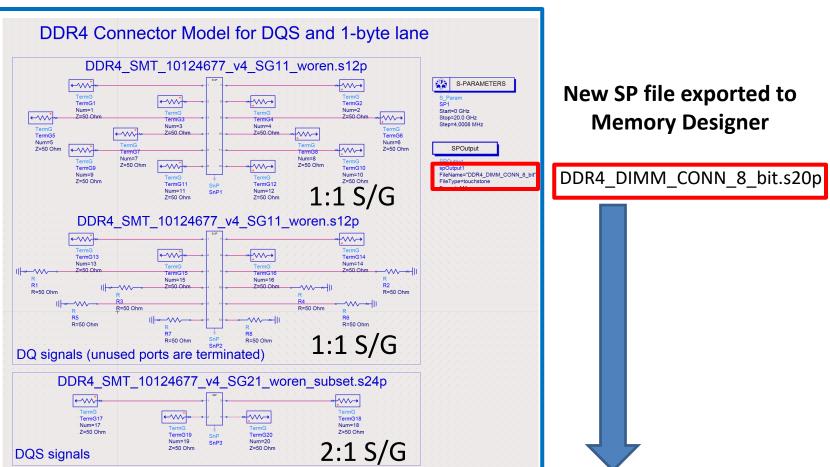

## **DIMM Connector Channel Model Setup**

Here is the better way to model your DDR4 Connector

To simulate complete DDR4 byte lane:

- (x2) 1:1 S/G combined with (x1) 2:1

S/G to create s20p model

- => Only one DIMM connector instance for DQ[0:7] and DQS0\_t/DQS0\_c

# **CONE** Channel Model Port Connection and IBIS Model Setup

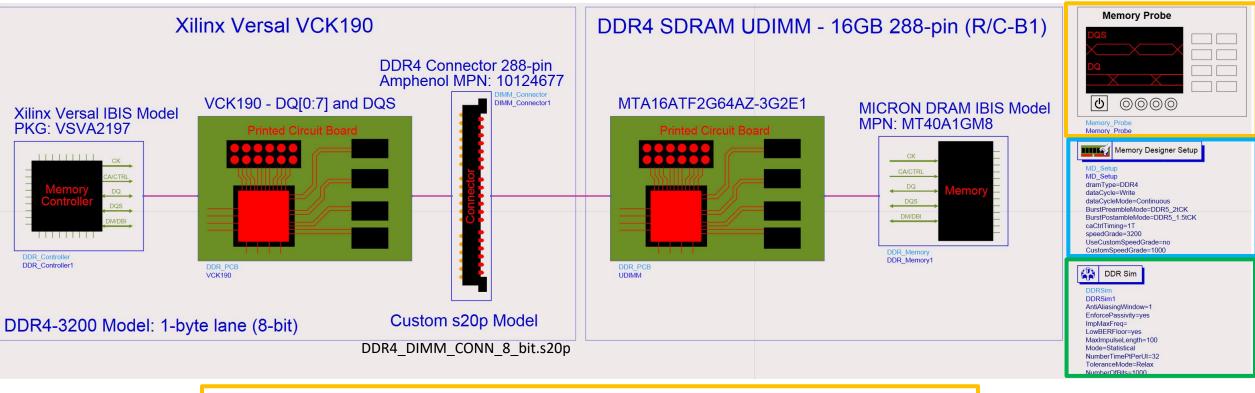

# DDR4 Channel Model Setup on VCK190 with UDIMM

Setup Memory Probe (e.g. Select signals, set parameters)

Select Correct Speed Grade and dataCycle

Ensure LowBERFloor = yes (to set simulation BER = 1E-16)

### >>>> READY TO SIMULATE!!!

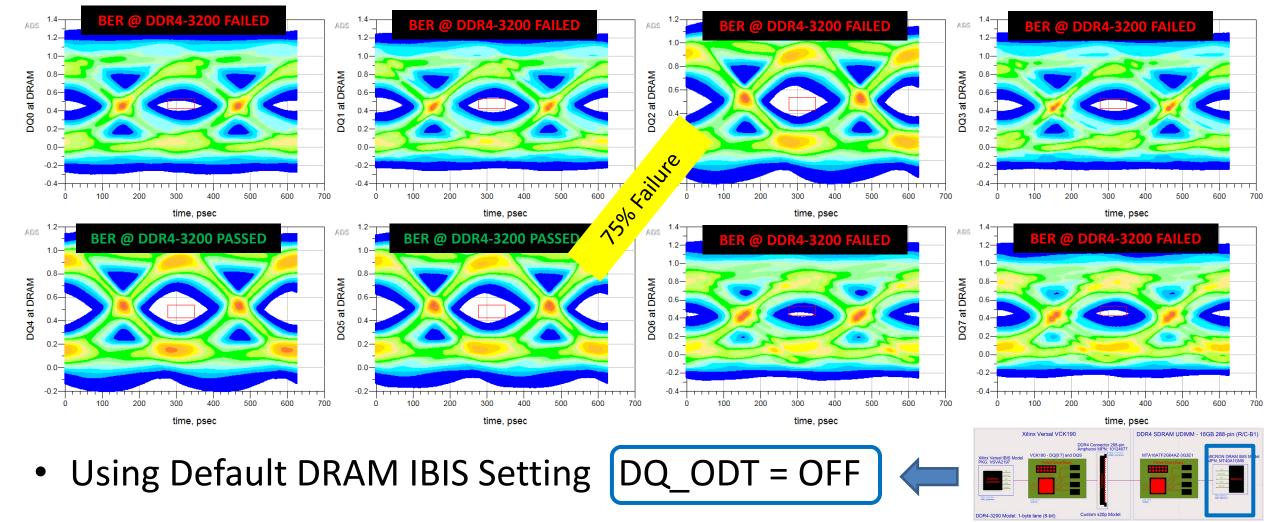

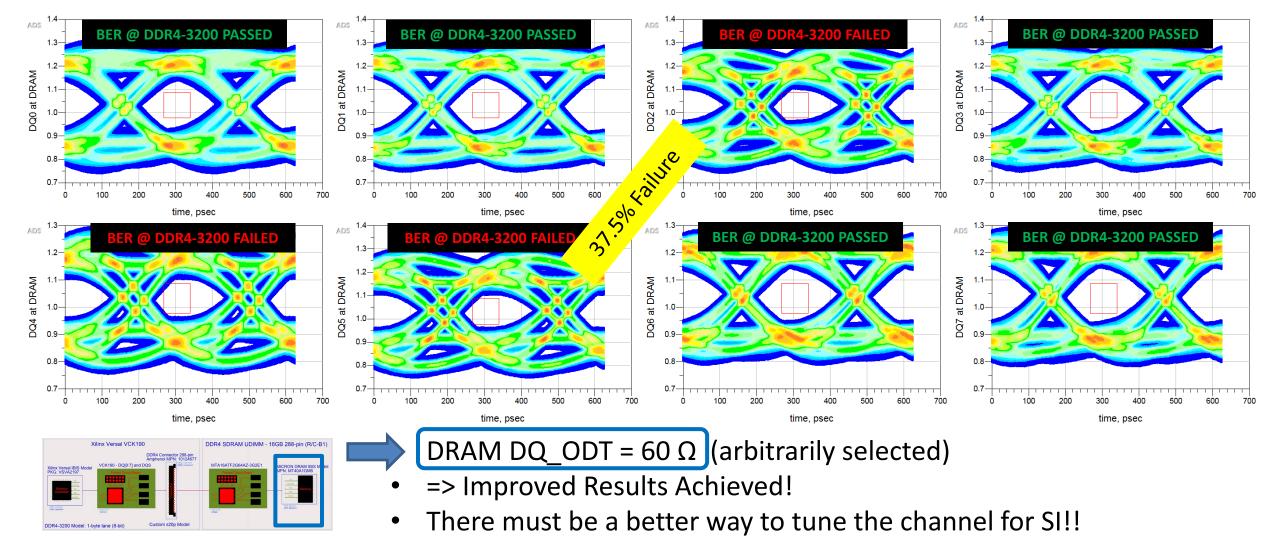

# Eye Diagram Initial Results DQ[0:7] for Write at DRAM

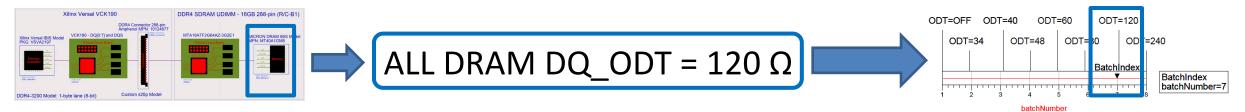

# ED EVE Diagram Results DQ[0:7] for Write at DRAM with ODT

\*\*DQ eye mask shown is for JEDEC DDR4-3200 to achieve BER 1E-16. Same eye mask for all test cases.

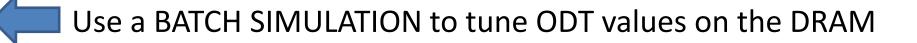

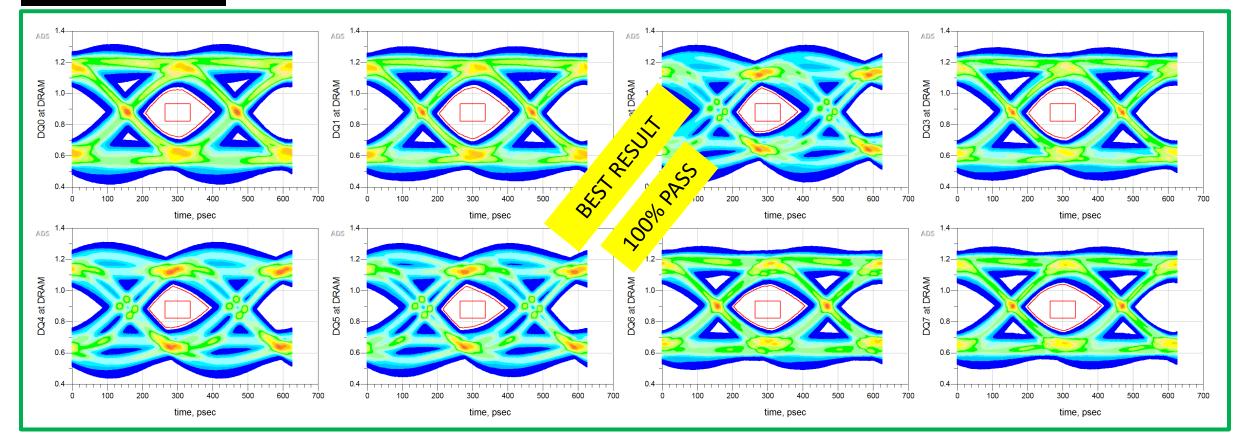

## Eye Diagram (DQ2) Write Results at DRAM - ODT tuning

BATCH SIMULATION

Var= Start=1.0 Stop=10.0 Step=1.0 Lin=

SweepArgument="DRAM\_ODT\_Sweep\_8bit.csv"

BatchSim1

Q2 at DRAN

ADS:

DQ2 at DRAM

UseSweepPlan=no Analysis[1]="DDRSim1" UseSweepModule=yes SweepModule="CSV List"

UseSeparateProcess=yes MergeDatasets=yes RemoveDatasets=no

\*\*DQ eye mask shown is for JEDEC DDR4-3200 to achieve BER 1E-16. Same eye mask for all test cases.

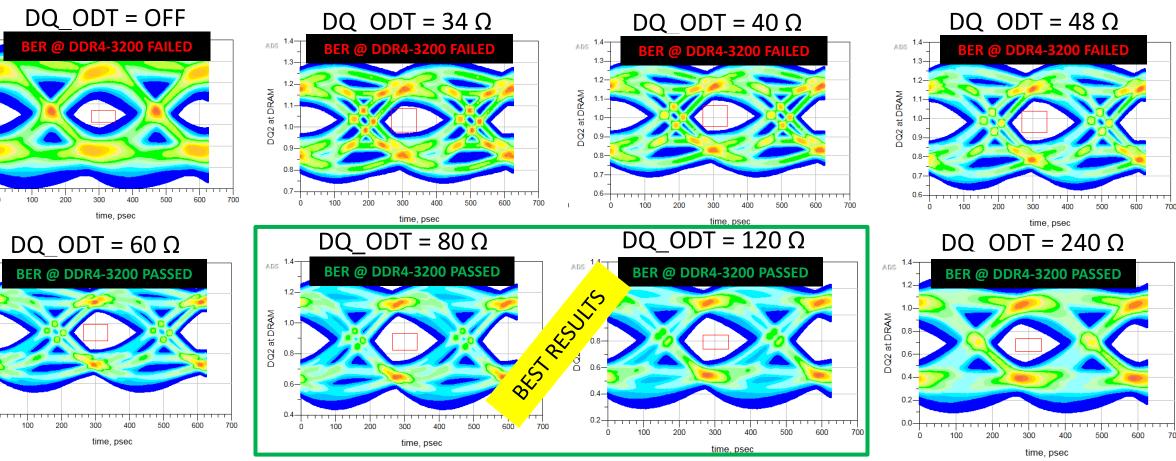

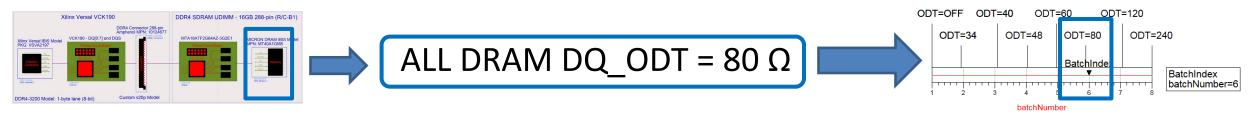

## Eye Diagram Results DQ[0:7] for Write at DRAM (post-tuning ODT)

BER @ DDR4-3200 PASSED

\*\*DQ eye mask shown is for JEDEC DDR4-3200 to achieve BER 1E-16. Same eye mask for all test cases. BER Contour shown for 1E-16

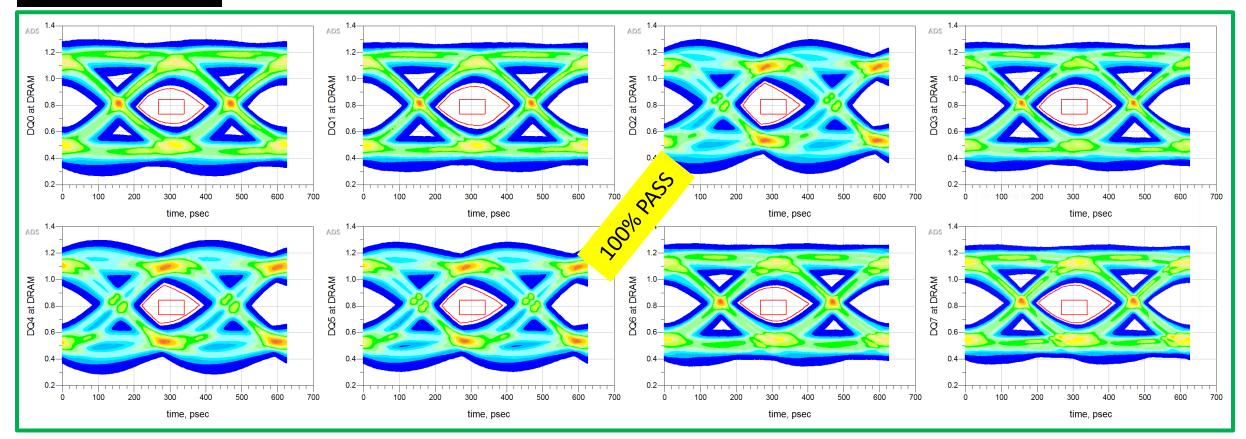

## Eye Diagram Results DQ[0:7] for Write at DRAM (post-tuning ODT)

BER @ DDR4-3200 PASSED

\*\*DQ eye mask shown is for JEDEC DDR4-3200 to achieve BER 1E-16. Same eye mask for all test cases. BER Contour shown for 1E-16

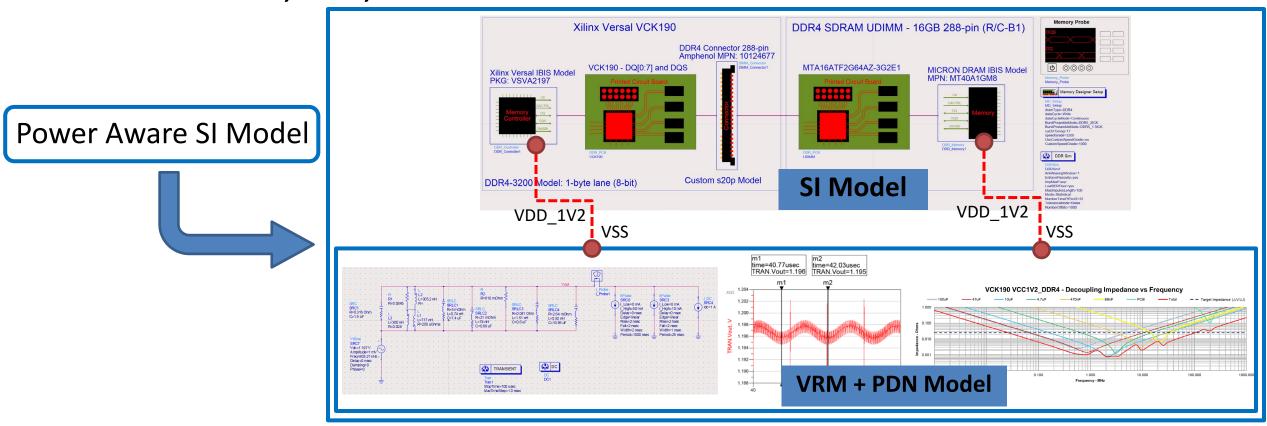

## What's Next

Simulate Power-Aware SI model

Simulate with CLK, CMD, ADD

- Includes PDN & Simultaneous Switching Noise (SSN)

- IBIS v5.0 or later necessary for Power-Aware (makes VDD/VSS pins available)

- Simulate complete DDR4 DQ bus

- => More switching signals = greater di/dt => greater SSN

- Enable EQ (CTLE)

- Jitter analysis

27

## **Summary and Conclusions**

- Always verify the PCB stack-up on your design!

- The VCK190 DDR4-3200 Solution Passes with UDIMM

- This model didn't include Jitter or other noise (SSN) from Power Sources

- Using a Power Aware SI model with a complete DQ bus will increase di/dt increasing ISI, jitter, and crosstalk

- Enabling EQ will be required to improve these results to meet DDR4 eye mask compliance

- DDR5 is here! => Smaller UI means more challenging SI problems

==> Shrinking margin, equalization required, correlated/non-correlated jitter tracking, unmatched IO conditions, etc.

# **Thank You for Attending**

### Any questions?

#### Let's connect!

Message me with subject line as "EDICon 2020" on:

## References

- 1. 46 Fascinating and Incredible YouTube Statistics <u>https://www.brandwatch.com/blog/youtube-stats/</u>

- 2. Facebook Users Are Uploading 350 Million New Photos Each Day, Cooper Smith <u>https://www.businessinsider.com/facebook-350-million-photos-each-day-2013-9</u>

- 3. Al servers will need much more memory. And you know who's going to be there? Yep, big daddy Micron, Chris Mellor https://www.theregister.co.uk/2018/05/23/micron\_analysts\_day/

- 4. The first DDR5 RAM modules promiss faster, more efficient PCs <u>https://www.engadget.com/the-first-ddr-5-ram-modules-are-80-percent-faster-than-ddr-4-122542315.html</u>

- 5. Versal AI Core Series VCK190 Evaluation Kit <u>https://www.xilinx.com/products/boards-and-kits/vck190.html</u>

- 6. Panasonic MEGTRON6 <u>https://industrial.panasonic.com/ww/products/electronic-materials/circuit-board-materials/megtron/megtron6</u>

- 7. Amphenol DDR4 Memory Module Sockets 288-pin DIMM Connector <u>https://www.amphenol-icc.com/</u>

- 8. ADS SIPRO <u>http://keysight.com/FIND/EESOF-ADS-SIPRO</u>

- 9. ADS PIPRO <u>http://keysight.com/FIND/EESOF-ADS-PIPRO</u>

- 10. DDR Simulation with Memory Designer and SIPro

https://www.youtube.com/watch?v=Qc1YjtzQfEU

https://www.youtube.com/watch?v=vHRg1o6bDLs

- 11. Losses in PCB Transmission Lines <u>https://www.protoexpress.com/blog/losses-in-pcb-transmission-lines/</u>

- 12. TN-00-33: Power Integrity Simulation with IBIS 5.0 Models Introduction <u>https://www.micron.com/-</u> /media/client/global/documents/products/technical-note/dram/tn\_0033\_ibis\_models\_power\_integrity\_simulation.pdf