# DDR4-3200 FPGA Based System with Interposer Power-Aware SI Simulation to Measurement Correlation

Benjamin Dannan, Northrop Grumman Randy White, Keysight Technologies

Benjamin Dannan (Northrop Grumman), Randy White (Keysight Technologies), Hermann Ruckerbauer (EyeKnowHow), HeeSoo Lee (Keysight Technologies)

#DesignCon

### **SPEAKERS**

#### **Benjamin Dannan**

*Technical Fellow & Staff Digital Engineer, Northrop Grumman* benjamin.dannan@ngc.com | northropgrumman.com

Benjamin Dannan is a Technical Fellow and a Staff Digital Engineer at Northrop Grumman Mission Systems. He has a BSEE from Purdue University, a Masters of Engineering in Electrical Engineering from The Pennsylvania State University, and graduated from the USAF Undergraduate Combat Systems Officer training school with an aeronautical rating. He received the prestigious DesignCon best paper award in 2020 and is a Keysight Certified Expert in ADS.

#### **Randy White**

Memory Solutions Program Manager, Keysight Technologies randy.white@keysight.com | keysight.com

Randy White is the Memory Solutions Program Manager for Keysight Technologies. He is focused on test methodologies for emerging memory technologies in server, mobile, and embedded applications. He has participated on many standards committees including PCI-SIG, USB-IF, SATA-IO, JEDEC to help define new test methodologies, and is currently the chair of the JEDEC JC40.5 Logic Validation subcommittee. He graduated with a BSEE from Oregon State University.

#DesignCo

informa markets

### **Today's Key Takeaways**

- To validate design performance on one of the first DDR4-3200 FPGA memory controllers as well as verify whether the design's electrical performance meets the JEDEC specifications through power aware simulations and measurements. These power aware simulations will look at the effects of SSN/SSO while including the effects of probe loading and a memory component interposer that is present during the measurement.

- This effort will look at EM extracted models from a 3D solver and show considerations to properly simulate with these models. While concluding with actual measurement correlation being done on the same simulated DDR4-3200 model.

### **Overview**

- Big Data Evolution

- Background on Interposers

- Measurement Setup with Interposer

- DDR4-3200 Measurement Results

- Simulation Setup

- Simulation Results

- DDR5 Channel Reflections and DFE Considerations

- DDR5 Golden Channel

- Next Steps

- Conclusion

- Questions

### **Big Data Evolution**

- The era of "Big Data"

- Global "Big Data" consumption increased 5000% between 2010 and 2020

- Data usage increased from 1.2 trillion GB to ~60 trillion GB

- By 2025, estimated that over 463 Exabytes (463,000 Petabytes) of data created each day (212,765,957 DVDs)

- Memory bandwidth continues performance scaling to meet requirements of the next-generation data center, IoT, and other highspeed applications

- Increased pressure from "Big Data" means SI engineers need to ensure high-speed memory designs will work

Source: The Evolution of Big Data https://www.qubole.com/blog/big-data-evolution/

#DesignCor

informa markets

### **Measurement Platform**

#### **XILINX VCK190**

- Xilinx Versal ACAP

- Validate DDR4-3200 Speed

- Hardened integrated DDR Memory Controller (DDRMC) + soft memory interface IP options

- AXI Traffic Generator used to exercise memory IP in both simulation and post-synthesis for hardware analysis

#DesignCo

Source: Xilinx.com

### **Background on DDR4 SSN**

#### WHAT IS SSN

#### Parallel single-ended signaling always suffers from Simultaneous Switching Noise (SSN)

- On Die and on package power delivery is never perfect, and will introduce VDD/GND dips/bounces that will be seen on the signals, as the driver is supplied by VDD and GND

- Single ended push/pull drivers will cause a significant  $\frac{dI}{dt}$  where any impedance (usually defined by inductance) will cause noise on the voltage rail that supplies a set of e. g. 11 output drivers (8\* DQ, 1\*DM/DBI, 2\*DQS)

- Differential interfaces (e. g. CML) usually are loading the power rails with more DC like current

- It is not just switching all TX outputs (SSO), but also when receiving and terminating many parallel signals this can introduce significant on-die noise, potentially disturbing internal circuitry.

- Experience shows, that quite often the Controller package is the limiting factor, as it is difficult to provide low inductive power planes, as an example:

- 11 signals per byte lane (DQ/DM/DQS) \* 9-byte lanes \* 2 channels = 198 output drivers that might switch in parallel!

#DesignCor

(informa markets

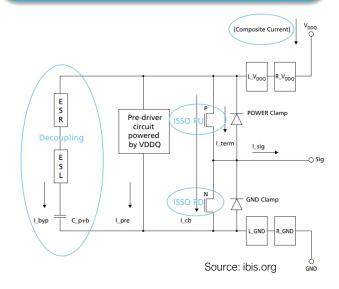

### **Background on DDR Power Aware Simulations**

#### SSN AND SSO IMPACTS TO DDR MODELING

- Simultaneous switching output noise, in single-ended signaling, is one of the major performance limiters as datarates scale higher

- Output drivers are major contributors of noise in the system

- $\circ~$  Power Supply noise and current profile are important in SSO simulations

- Latest generation DDR4 and next-generation DDR5 solutions, simulations need to include SSN, and therefore power-aware SI simulation modeling is necessary.

- Today's SI engineers need to be able to do both SI and PI when it comes to modeling DDR interfaces

PI Modeling requires [Composite Current], [ISSO PU], [ISSO PD], & IBIS ISS on-die decoupling circuit model

This is defined in the IBIS Model

#DesignCon

() informa markets

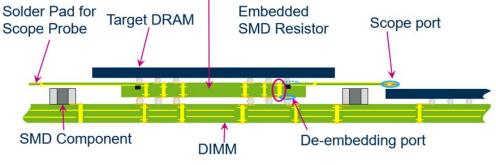

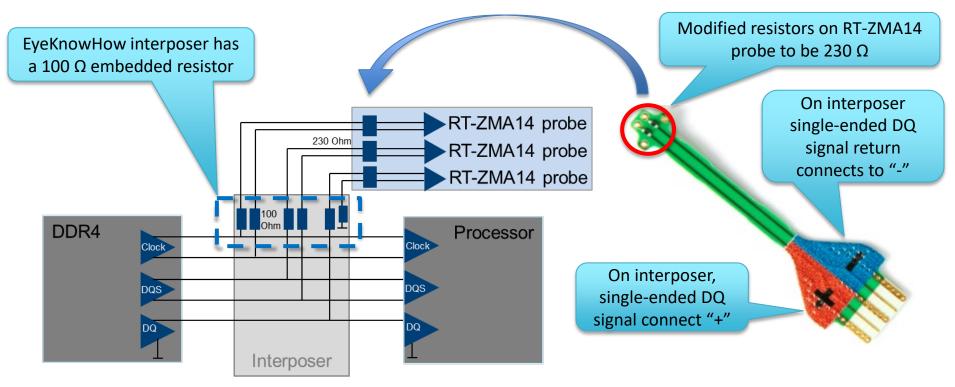

## **Background on Interposers**

- **BGA** component interposer for signal access

- Interposer model

- 2- or 4-port for simulation loading

- 3- or 6-port for oscilloscope de-embedding

- Probing side includes series resistor to minimize reflections

- Different types of active scope probes will react differently 0 (e.g. due to the change of source impedance of the DUT)

- Dependent on the type of probe a modification of the input 0 resistors is required (see next slide)

#### EyeKnowHow Interposer

Source: EyeKnowHow.de

**APRIL 5 – 7, 2022**

#DesignCon

q

#DesignCon

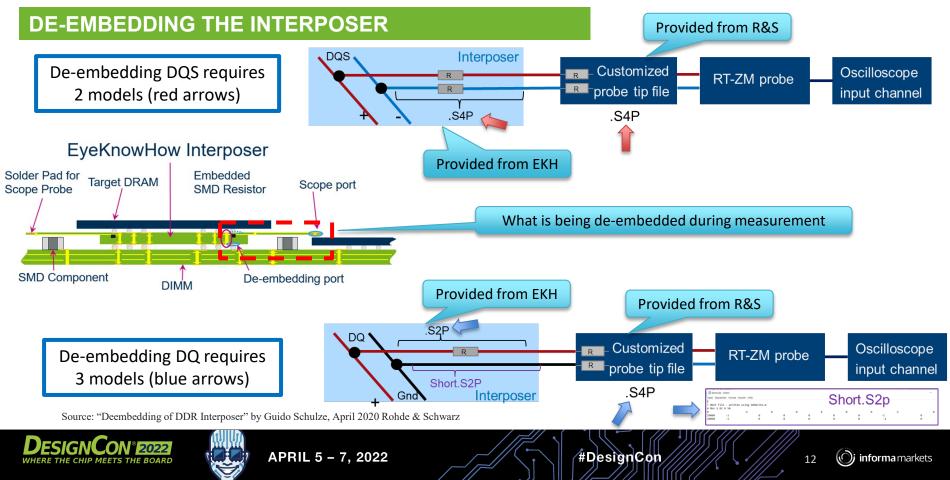

Source: "Deembedding of DDR Interposer" by Guido Schulze, April 2020 Rohde & Schwarz

10

informa markets

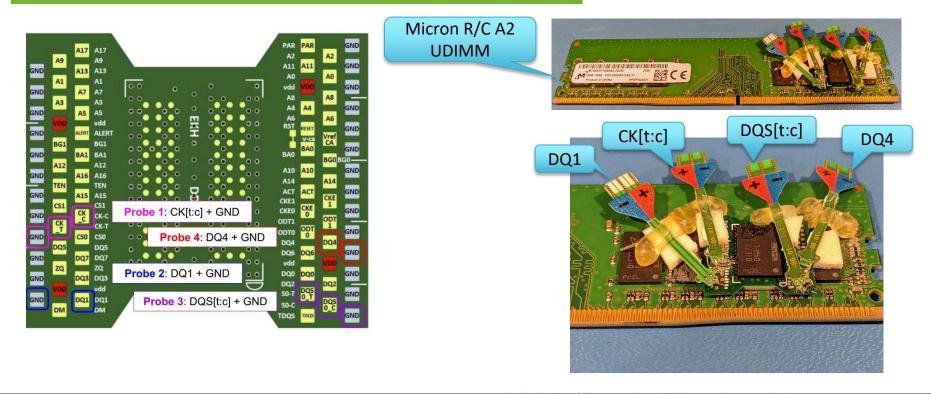

#### **INTERPOSER PROBE SETUP WITH UDIMM**

#DesignCon

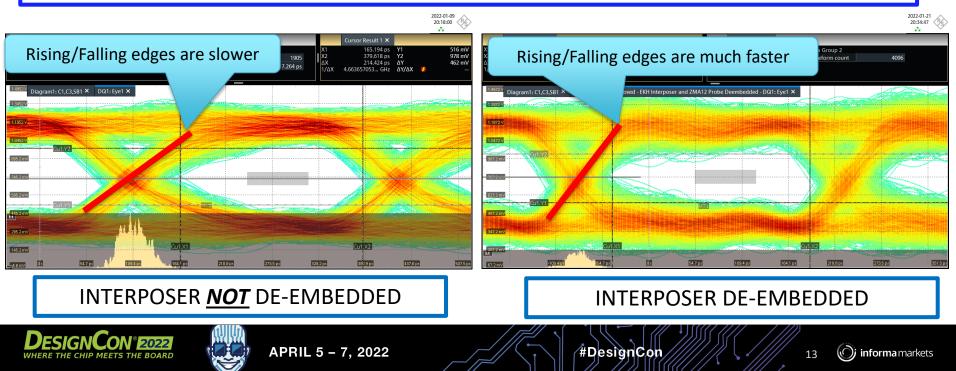

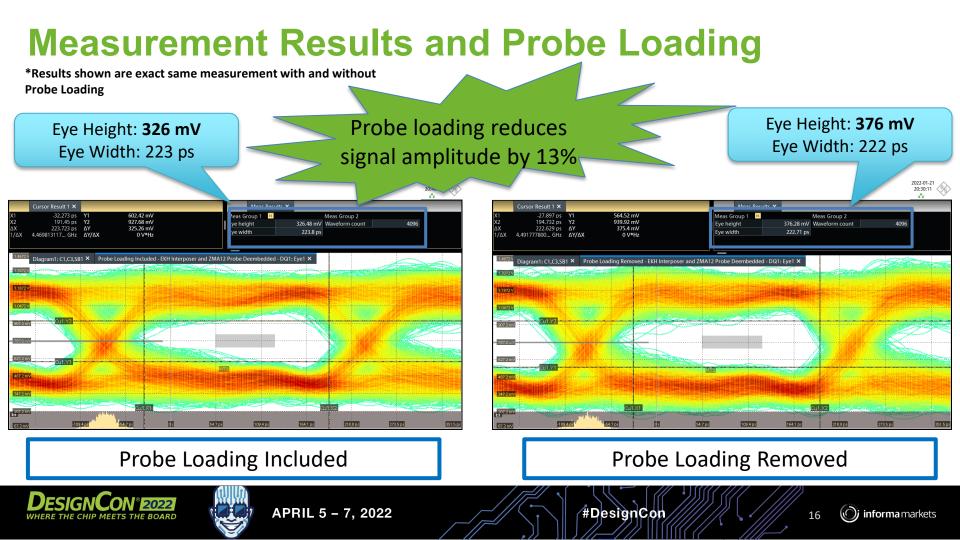

#### WHY DE-EMBEDDING THE INTERPOSER MATTERS

\*Both measurement results shown are without Probe Loading

BY DE-EMBEDDING THE CORRECT EYE SHAPE CAN BE CAPTURED DURING MEASUREMENT!

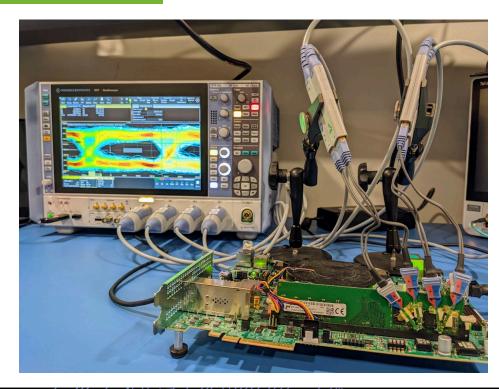

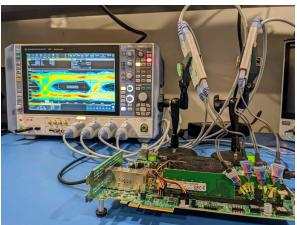

#### MEASUREMENT PLATFORM WITH R&S RTP164 SCOPE

- R&S RTP164 16GHz BW Oscilloscope

- RT-ZM160 16GHz Modular Probe

- RT-ZMA14 Probe Tip (modified w/230Ω resistor)

APRIL 5 – 7, 2022

#DesignCor

14

informa markets

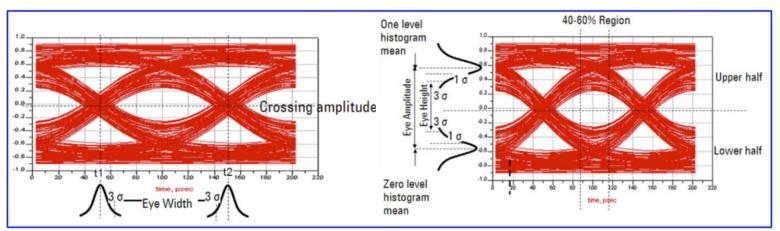

### **Eye Width and Eye Height Measurements**

<u>R&S RTP164</u> and <u>Keysight PathWave Memory Designer</u> use the same equations to calculate Eye Width and Eye Height

Eye Width =

$$(t_2 - 3 \cdot \sigma_2) - (t_1 + 3 \cdot \sigma_1)$$

#DesignCon

*Eye Height* = (*Level*1 -  $3 \cdot \sigma_{LEVEL1}$ ) - (*Level*0 +  $3 \cdot \sigma_{LEVEL2}$ )

SOURCE: http://literature.cdn.keysight.com/litweb/pdf/5989-9453EN.pdf

15 🔘 i

### **Measurement Results**

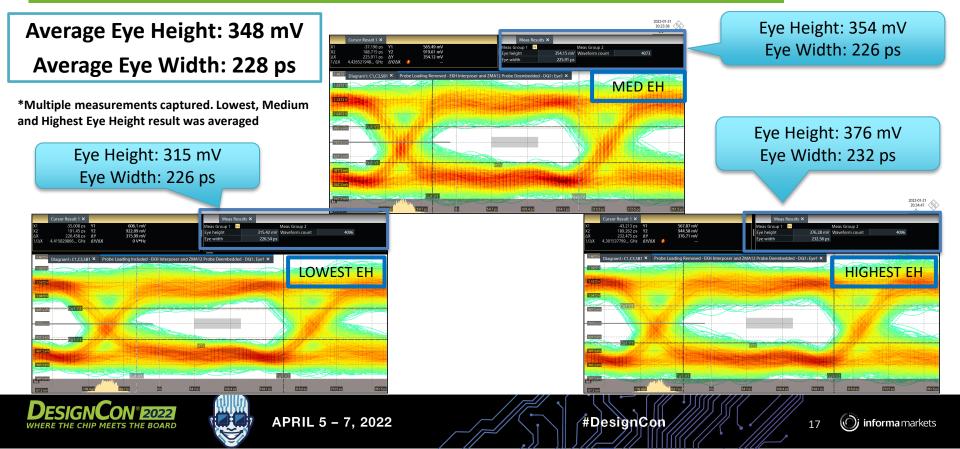

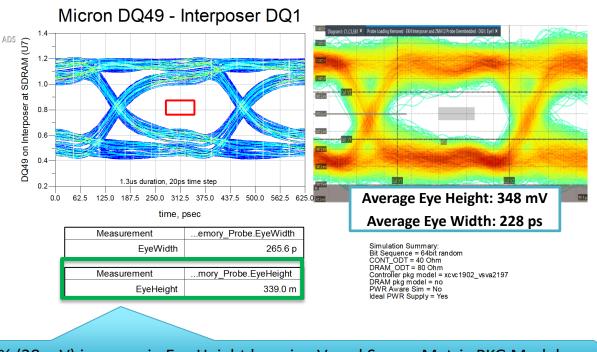

#### AVERAGE EYE HEIGHT AND EYE WIDTH – PROBE LOADING REMOVED

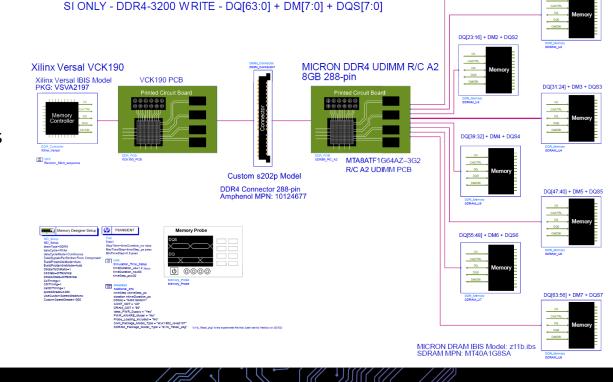

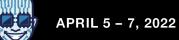

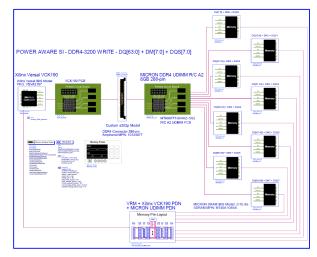

#### SI ONLY MODEL – DDR4-3200

Simulation Settings

- DDR4-3200 Speed Grade

- Pattern: 64-bit PRBS pattern across all 64 data bits

- SIM Duration: 1.3usec = 4160 bits across the channel

- Transient time step = 20ps

#DesignCon

18

DQ[7:0] + DM0 + DQS0

DQ[15:8] + DM1 + DQS1

DQS DWDBI

DDR\_Memo

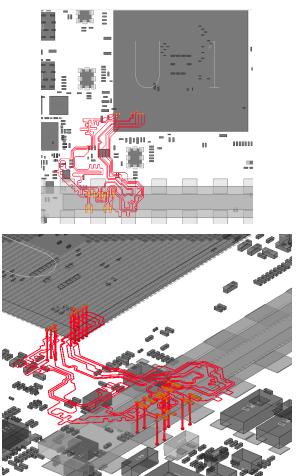

#### VCK190 PCB AND R/C A2 UDIMM PCB STACKUPS

#### SIPro used to create EM extracted models for SI nets

- ALL 8-byte lanes for DQ, DM, DQS nets were co-extracted together, on the VCK190 and UDIMM PCBs, to account for the net-to-net coupling

- PIPro used to create EM extracted models for PDN on VCK190 and UDIMM

- All EM extracted models were fully passive and only some models had minor causality violations

- VCK190 PCB stack-up total thickness is 70.98 mil

- o 18 total layers

- UDIMM R/C A2 PCB stack-up total thickness is 1.442 mm (meets JEDEC UDIMM standard for thickness)

- o 8 total layers

NOTE: JEDEC UDIMM standard thickness is 1.4 +/-0.1 mm without solder mask

SOLDERMASK (3.5) MEG6-G\_PREG\_1078HF(64) (3.4) ORAL TOPLI SEL DRAL TOP L2 GNDS MEG6-G\_CORE\_1078 (3.58) MEG6-G\_PREG\_1078HF(68) (3.34 EOF 14 GIES EG6-G\_CORE\_1078 (3.58) MEG6-G\_PREG\_1078HF(68) (3.34 ETCH\_LS\_SIG EG6-G CORE 1078 (3.58) \$0.25 UDIMM PC4-3200 R/C A2 PCB EGE-G\_PREG\_1078HF(68) (3.34) (5+1.8) mil 47.65 Stack-up EOH 18 GIDA G6-G\_CORE\_1035 (3.39) 42.35 EGE-G PREG 2X1035H F(70) (3.2 40.35 ECH LIS PUR POLYIMEDE (2.6) G6-G CORE 1035 (3.39) 101 10 FR-4 (4.2) (0.065+0.015) millim EGE-G DREG 1078HE(68) (3.34 DRUL\_TOP\_BOTTOM EON 112 000 EICH #1 1.292 FR-4 (4.2) (0.076+0.015) millime G6-G\_CORE\_1078 (3.58) EICH SS FR-4\_1 (4.5) (0.429+0.015) millim EGE-G PREG 1078HF(68) (3.3 EOLIN SS EICH P.4 FR-4\_2 (4.5) 0.076 millime FR-4\_2 (4.5) (0.425+0.015) millim EGE-G DREG 1078HE(68) (3.1 TTOI P 101 LS 00 EOL IN SOL EGE-G CORE 1078 (3.58) DRILL LIS SIGE ROTTO MEG6-G PREG 1078HF(64) (3.4 FR-4 (4.2) (0.065+0.015) millim POLYINEDE (2.6) (0.025+0.045) mill SOLDERMASK (3.5

Xilinx VCK190 PCB Stack-up

#DesignCon

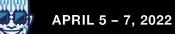

#### SETTING UP UDIMM CONNECTOR MODEL

- Amphenol provides 12-port SG & 24-port SS touchstone models for DDR4 288-pin DIMM connector

- 202-port custom model generated for 9-byte lanes with CLK

- A limitation is simulated crosstalk between byte lanes is limited at the connector to only signals within 12-port SG and 24-port SS model.

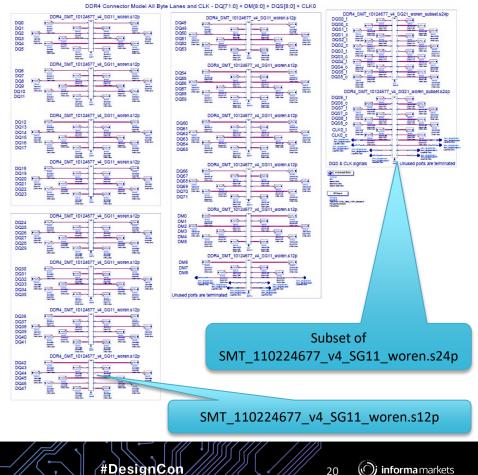

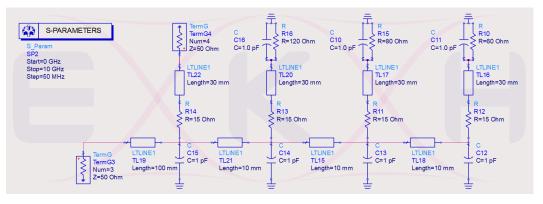

#### POWER AWARE SI MODEL – DDR4-3200

Simulation Settings

- DDR4-3200 Speed Grade

- Pattern: 64-bit PRBS pattern across all 64 data bits

- SIM Duration: 1.3usec = 4160 bits across the channel

- Transient time step = 20ps

APRIL 5 – 7, 2022

#DesignCon

DQ[7:0] + DM0 + DQS0

DQ[15:8] + DM1 + DQS1

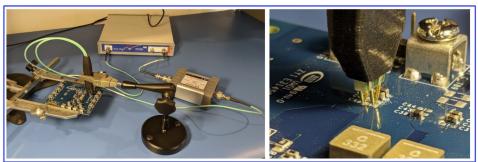

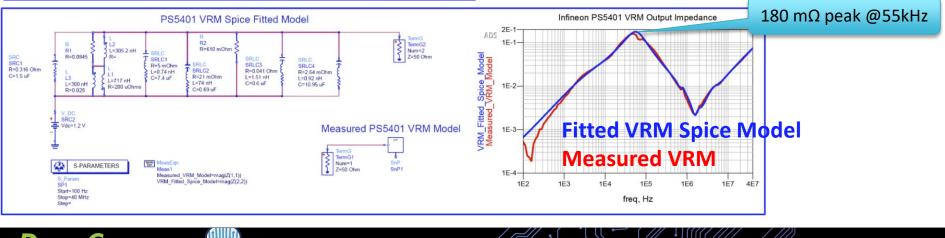

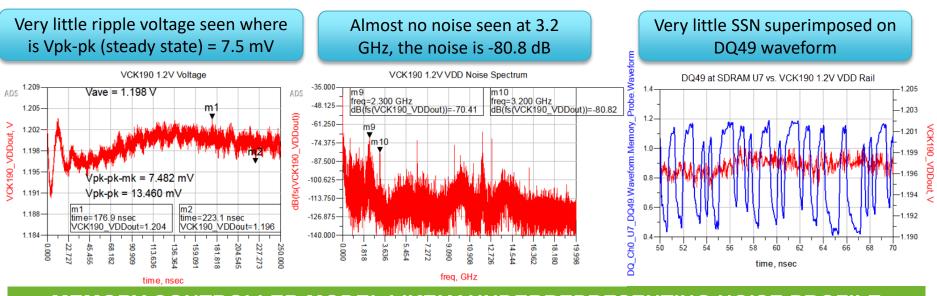

#### **VCK190 VRM CHARACTERIZATION**

**APRIL 5 – 7, 2022**

Omicron Lab Bode 100

#DesignCon

- Picotest P2102A-1X 2-port Probe

- Picotest J2102B Common Mode Transformer

(i) informa markets

- Picotest PDN Cable BNC-BNC 0.25m

- DUT Infineon PS5401 EVAL Kit

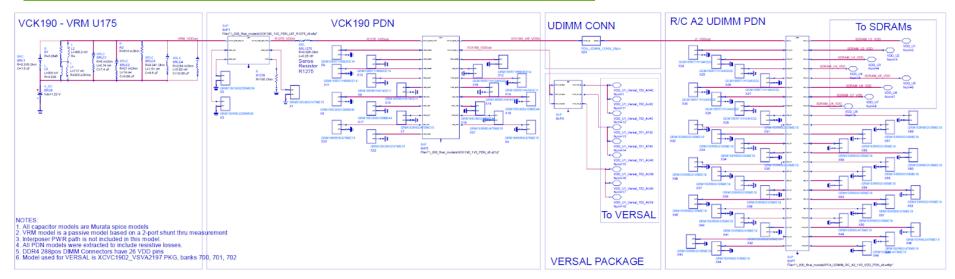

#### VRM + VCK190 PDN + R/C A2 UDIMM PDN

#DesignCor

- All capacitor models are Murata spice models

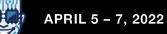

- Versal VCCO PKG Model included for banks 700, 701, 702 used for DDR4

- UDIMM Connector model includes 26 VDD pins to ensure accurate spreading inductance

- UDIMM connector model is assumed to include GND losses

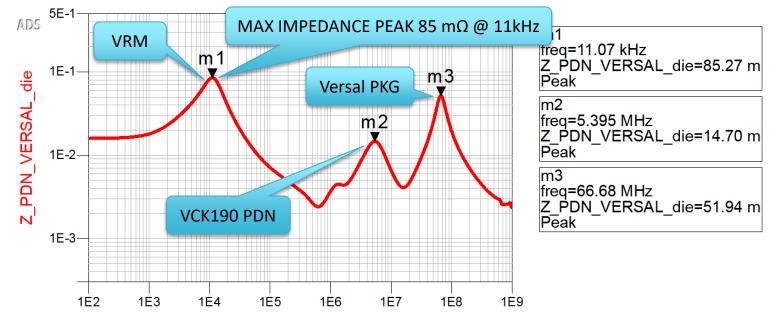

#### PDN LOOKING FROM VERSAL DIE

#### PDN - VCK190 with R/C A2 UDIMM - Looking from Versal Die

#DesignCon

#### VERSAL DIE AND PKG – VCCO BANK 700, 701, 702 ANALYSIS

In Versal IBIS model, capacitance per power pin (AJ42, AT43, AV39) are all about 50 pF, which is unusually high for the C\_pkg

Ensures a reasonable amount of on-die decoupling has been included in Memory CTL to support SSO

### **Background on ODT Levels**

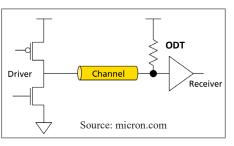

#### HOW ODT WORKS WITH DDR4

- On-Die Termination (ODT) for reducing reflections from discontinuities

- Source (driver) + Load  $\rightarrow$  voltage divider network with pseudo-open drain

#### POD I/O Buffer

## **Background on ODT Levels**

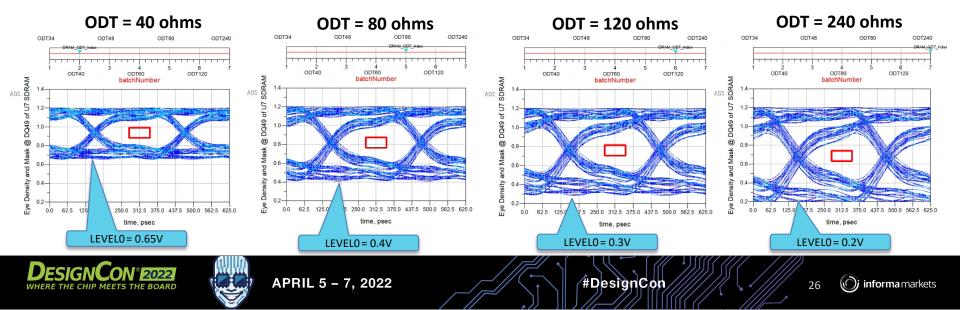

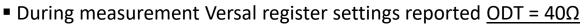

#### XILINX VERSAL REPORTED ODT VALUE DURING MEASUREMENT

Measurement with Xilinx Versal during DDR4 write shows  $Vx_{IEVELO} = ~400 \text{ mV}$

#### For simulation correlation to measurement a minimum ODT setting of 80 $\Omega$ is required

#DesignCon

(informa markets

#### SI ONLY – MEM CTL SP DISTRIBUTED PKG MODEL

- Results shown with optimized eye using ODT = 80Ω

- Versal distributed SP model included

- SDRAM IBIS model v2.4

RON DOR4 UDIMM

MICH ON ORAM SHI MARK

DRAM PKG model not included

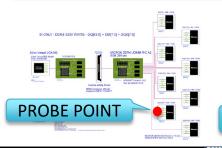

#### Result shown is with Versal S-parameter Distributed PKG Model

#DesignCon

**PROBE POINT**

SI CNLY - DDR4-3200 WRITE - DQ83:0] + DM[7:0] + DQ8[7:0

(C

#### SI ONLY - MEM CTL SPARSE MATRIX PKG MODEL & NO DRAM PKG MODEL, DRAM ibis v2.4

- Results are shown with optimized eye using ODT = 80Ω

- Versal sparse matrix PKG model included

- SDRAM IBIS model v2.4

- DRAM PKG model not included

ACRONOR DRAME BIR Made

13% (38 mV) increase in Eye Height by using Versal Sparse Matrix PKG Model

**PROBE POINT**

SI ONLY - DDR4-3200 WRITE - DQ83:0] + DM[7:0] + DQ8[7:0]

APRIL 5 – 7, 2022

#DesignCon

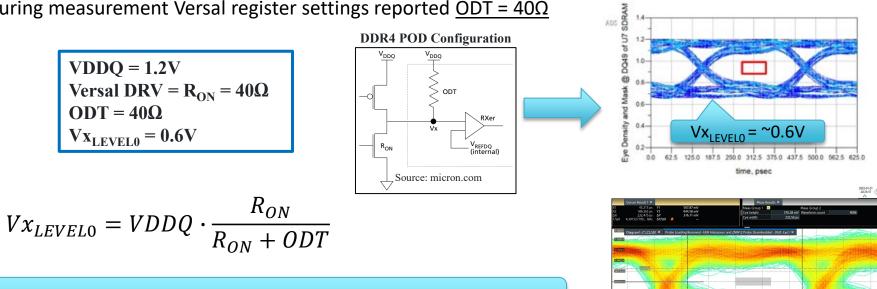

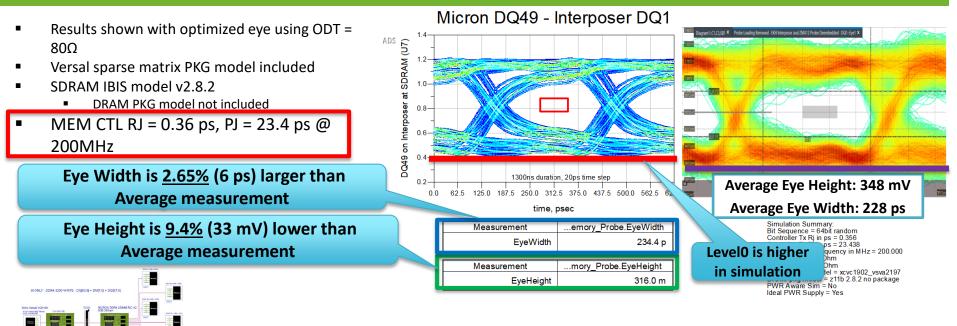

#### SI ONLY - MEM CTL SPARSE MATRIX PKG MODEL & NO DRAM PKG MODEL, DRAM ibis v2.8.2

5

SDRAM

on Interposer at

0.4 DQ49

0.2

Micron DQ49 - Interposer DQ1

- Results are shown with optimized eye using ODT = 80Ω

- Versal sparse matrix PKG model included

- SDRAM IBIS model v2.8.2

- DRAM PKG model not included

# Level0 point is lower in measurement vs. simulation

1.3.us duration, 20ps time step

1.3.us duration, 20ps time step

0.0

62.5

125.0

187.5

250.0

312.5

375.0

437.5

500.0

562.5

625.0

100

time, psec

Measurement

...em ory\_Probe.EyeWidth

EyeWidth

265.6

p

Measurement

...mory\_Probe.EyeHeight

Status

...mory\_Probe.EyeHeight

Status

...mory\_Probe.EyeHeight

Average Eye Height: 348 mV Average Eye Width: 228 ps

1.(3.581 X Probe Loading Removed - EKH Interposer and ZMA12 Probe Deembedded - DQ1: Eve

Sim ulation Summary: Bit Sequence = 64bit random CONT\_ODT = 40 Ohm DRAM\_ODT = 80 Ohm Controller pkg model = xcvc1902\_vsva2197 DRAM pkg model = no PWR Aware Sim = No Ideal PWR Supply = Yes

0.6% (2 mV) increase in Eye Height when using newer DRAM ibis model v2.8.2

#DesignCor

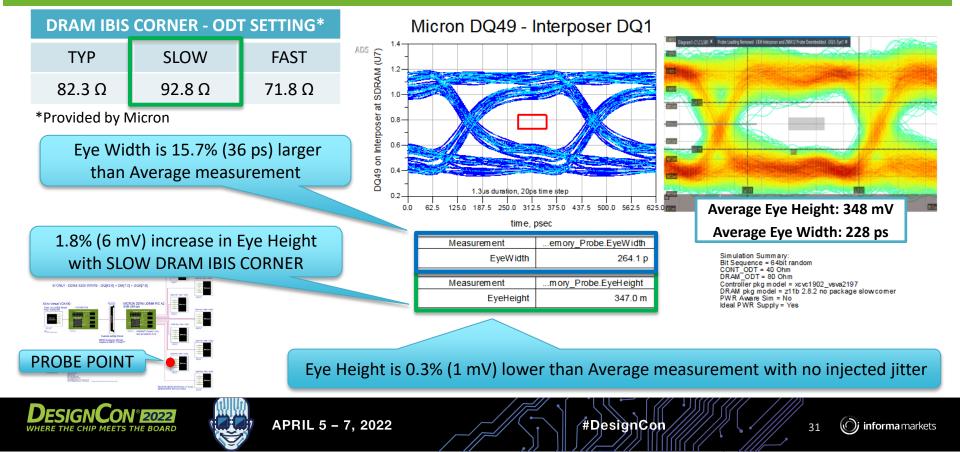

#### SI ONLY MEM CTL SPARSE MATRIX PKG MODEL, NO DRAM PKG MODEL, DRAM ibis v2.8.2, DRAM SLOW CORNER

# **Simulation Model Results with Injected Jitter**

#### SI ONLY MEM CTL SPARSE MATRIX PKG MODEL, NO DRAM PKG MODEL, DRAM ibis v2.8.2, DRAM SLOW CORNER

Eye Width correlates to Measurement! The SDRAM ODT model prevented us from matching Eye Height measurement with injected Jitter.

**PROBE POINT**

**APRIL 5 – 7, 2022**

#DesignCon

32

BEST RESULT

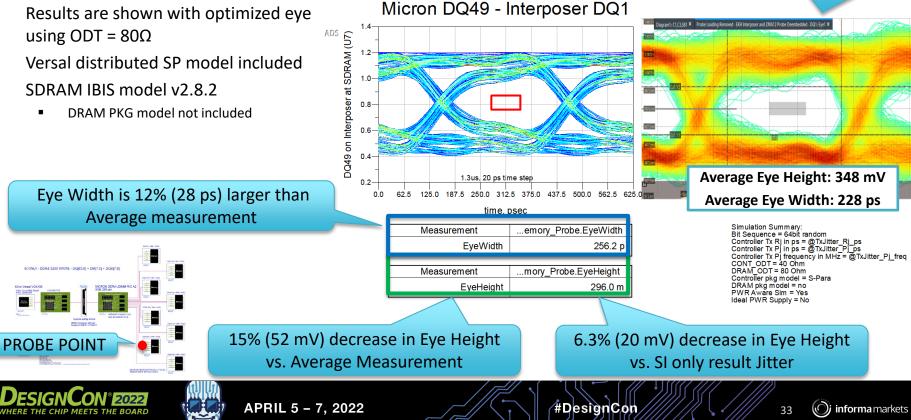

#### **POWER AWARE SI RESULTS**

- Results are shown with optimized eye using ODT =  $80\Omega$

- Versal distributed SP model included

- SDRAM IBIS model v2.8.2

Measurement model includes SSN from SSO

#### POWER AWARE SI RESULTS

Power Aware SI Model includes 64 bits switching in PRBS pattern

#### MEMORY CONTROLLER MODEL LIKELY UNDERREPRESENTING NOISE PROFILE

#DesignCon

(informa markets

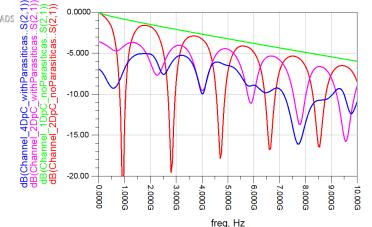

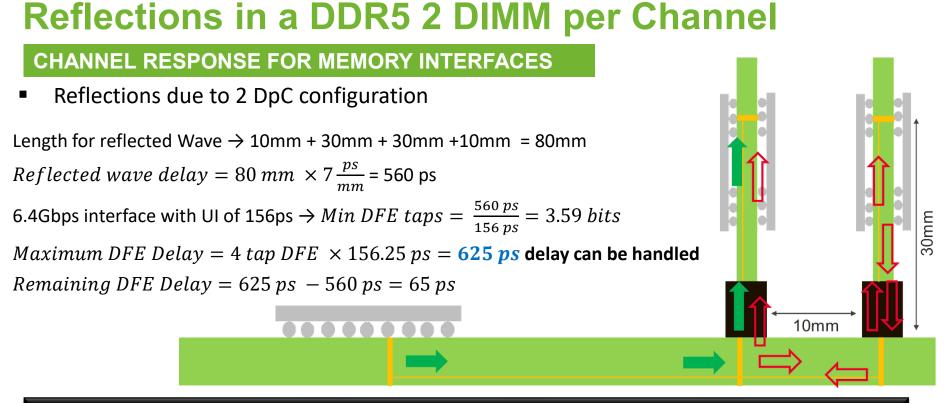

# **Equalizer: Impact of Topology**

#### CHANNEL RESPONSE FOR MEMORY INTERFACES

- Channel Responses for a higher number of DIMMs per Channel

- R-DIMM does have a series Resistor on DIMM

- Stub is too long to compensate with 4-tap DFE (blue S21 plot)

- → It will be difficult (near impossible) to implement 4 DIMM systems at high speed!

4 DIMM slots: 10mm DIMM2DIMM + 30mm DIMM stub

#DesignCon

Large DRAM subsystems will never get a P2P environment and will therefore always have to deal with reflections!

#DesignCo

### **The Future of DDR Simulation**

#### **THE DDR5 GOLDEN CHANNEL**

#DesignCon

Source: Evolution of High-Speed Server and Computing Interfaces - https://keysightevent.com/kw2019/handout/b5

### **Next Steps**

- Update Versal IBIS model with ISSO PU and PD curves to achieve correlated power-aware SI model to measurement

- Explore DDR5 paths to do power-aware SI simulation using AMI models

- IC vendors and EDA software tools need a suitable solution that allows power-aware SI and AMI modeling with equalization

- Explore effects of SSN with State-Space Average VRM model

- Explore effects of this noise generated through the return path at the UDIMM connector, Versal package, VCK190 PCB, and UDIMM PCB.

- Drive industry to implement a Golden reference channel + DFE (DDR5)

APRIL 5 – 7, 2022

#DesignCo

38 🤅

informa markets

# Summary

#### Validated DDR4-3200 design

- Correlated SI only simulation with jitter to measurement

- Power-aware SI models

- Interposer-based measurement setup

#### Key learnings

- Must include de-embedding & probe loading effects

- Vendor IBIS model importance

- Vendor package models matter!

- Chip vendors need to work harder to provide more accurate models

#DesignCo

39 🔘

# Thank you!

#### **QUESTIONS?**

APRIL 5 - 7, 2022

**#**C

### **Acknowledgements**

- Picotest: Steven Sandler

- Rohde & Schwarz: Jason Ruffing, Mike Schnecker

- Keysight: Stephen Slater, Nacim Bravo

- Xilinx: Taylor Maddix, Ryan Arp, Fran Olveri, Jon Schimek, Sam Hendrix, John Rinck

- Micron: Justin Butterfield

#### References

- Eye Diagram Measurements in Advanced Design System http://literature.cdn.keysight.com/litweb/pdf/5989-9453EN.pdf 1.

- 2. "Deembedding of DDR Interposer" by Guido Schulze, April 2020 Rohde & Schwarz

- Evolution of High-Speed Server and Computing Interfaces https://keysightevent.com/kw2019/handout/b5 3.

- 4. Rohde & Schwarz - RTP164, 16GHz Bandwidth Oscilloscope - https://www.rohde-schwarz.com/us/product/rtp-productstartpage\_63493-469056.html

- Rohde & Schwarz Probe Amplifier Module 16 GHz Bandwidth RT-ZM160 https://www.rohde-schwarz.com/us/product/rt-zm-productstartpage 63493-5. 326208.html

#DesignCor

- 6. Rohde & Schwarz - Flex Connect solder-in Probe Tips 16GHz Bandwidth - RT-ZMA14 - https://www.rohde-schwarz.com/us/product/rt-zmproductstartpage 63493-326208.html

- Xilinx VCK190 https://www.xilinx.com/products/boards-and-kits/vck190.html 7.

- 8. Picotest P2102A - 2 Port PDN Transmission Line Probe - https://www.picotest.com/products PDN Probe.html

- 9. Picotest J2102B-N – Common Mode Transformer - https://www.picotest.com/products J2102B.html

- Picotest PDN Cable® https://www.picotest.com/pdn-cable.html 10.

- Keysight N2787A 3D Probe Positioner https://www.keysight.com/us/en/product/N2787A/3d-probe-positioner.html 11.

- 12. Infineon EVAL\_PS5401-INT - https://www.infineon.com/cms/en/product/evaluation-boards/eval\_ps5401-int/

- 13. Amphenol DDR4 DIMM Connector, https://www.amphenol-icc.com/ddr4-101246770221r11lf.html

- 14. Modeling On-Die Power Supply Decoupling - https://ibis.org/summits/feb12/wolff.pdf