©2021, Northrop Grumman

# Project X DDR4-2400 Signal Integrity Analysis

Staff Digital Engineer

April 8, 2021

NORTHROP

# **Outline**

- Design Assumptions

- System Models

- Single Byte Lane DQ[7:0] Channel Analysis

- Single Byte Lane DQ[7:0] Write Results

- 2 Byte Lane DQ[15:0] + DM[1:0] + DQS1 + DQS0 Read/Write Results

- 4 Byte Lane DQ[31:0] + DM[3:0] + DQS[3:0] + CLK0 Write Results

- A[7:0] Write Results with UDIMM

- A[7:0] Write Results with RDIMM

- Follow Up Questions

NORTHRO

# **Design Assumptions**

- Simulation Temp: Room Temp (25°C)

- Not Power Aware SI Power Integrity is not included in any of these models

- No DFE or EQ enabled

- Simulation Setup

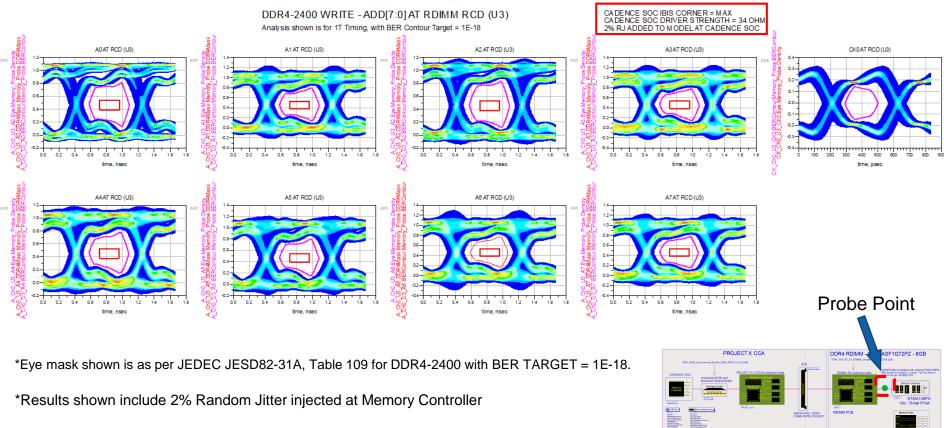

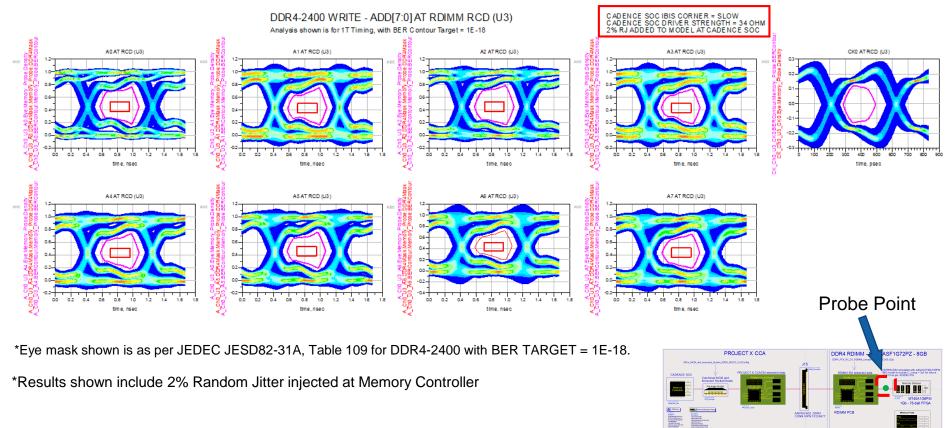

- Unless otherwise stated, all Models will include 2% RANDOM JITTER (RJ) => 0.02 UI

- At the memory controller for WRITE cycle RJ = 8.333 ps for DQ, 4.17 ps for all other nets

- At the SDRAM for READ cycle RJ = 8.333 ps for DQ, 4.17 ps for all other nets

- All Simulations shown were done in ADS using Memory Designer

- Using ADS Memory Designer Statistic based simulation and bit-by-bit simulations

- Unless otherwise stated

- IBIS Corner setting = MAX

- Unless stated otherwise models shown are for MAX IBIS corner type

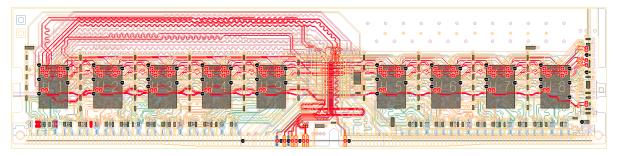

- Unless otherwise stated, all EM extractions for Project X CCA, UDIMM CCA, and MCM model were done using SIPro

- Simulation models as shown include crosstalk as part of simulation as per MCM, Project X CCA, UDIMM CCA EM extraction configurations. Any included crosstalk is limited per connector and socket models.

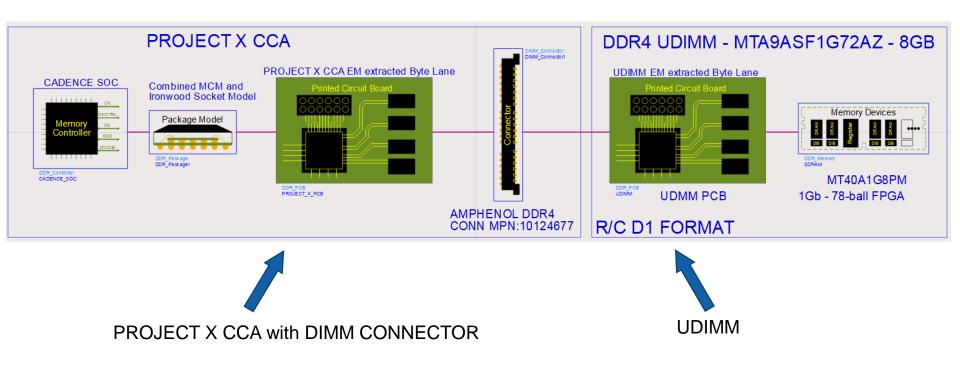

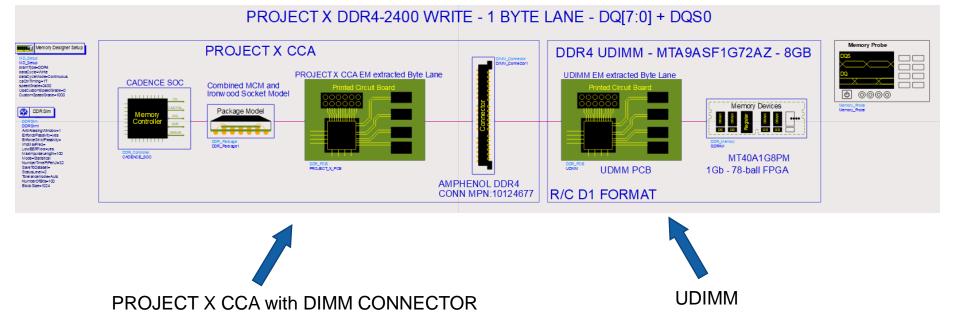

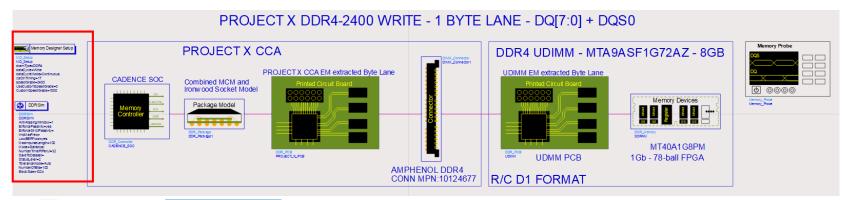

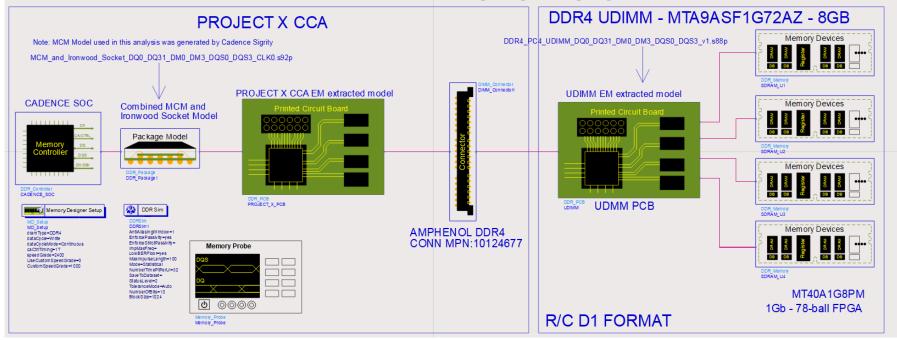

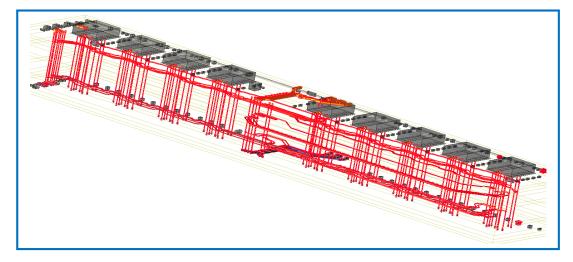

# **Project X CCA to UDIMM Model**

# **System Models - IBIS Models - CADENCE ASIC**

| CADENCE MCM (ASIC) MPN: 828RA72                                                                        |                                                                                    |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| IBIS file created by T2B Version 17.2.9.04121.123020 009<br>  Cadence Design Systems, Inc. 2011        |                                                                                    |

| [IBIS ver] 5.1<br>[File name] gf_12lp_ddr4.ibs<br>[File Rev] 1.0<br>[Date] December 4, 2019            | Original Model had to be edited to include multiple additional pins for simulation |

| *************************************                                                                  |                                                                                    |

| [IBIS ver] 5.1<br>[File name] gf_12lp_ddr4_edited_1v2.ibs<br>[File Rev] 1.2<br>[Date] January 25, 2021 | Model used for simulation                                                          |

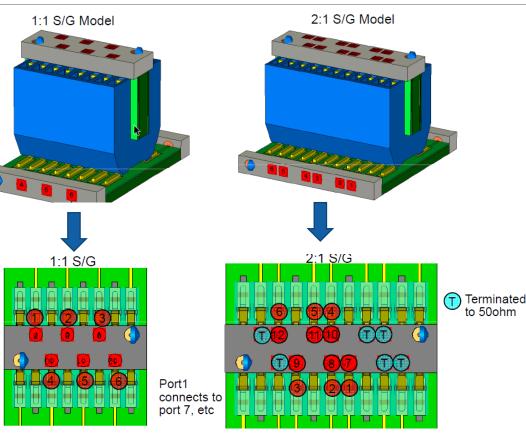

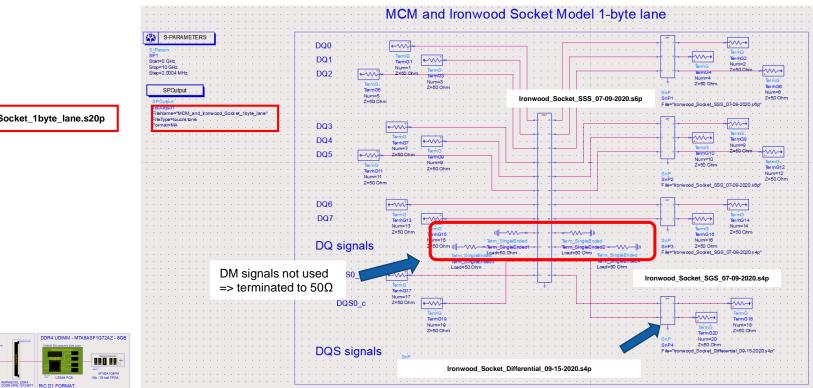

# **System Models – Socket Model**

6

NORTHROP GRUMMAN

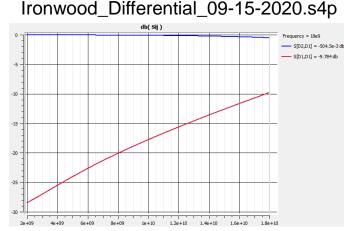

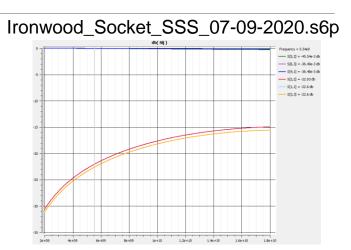

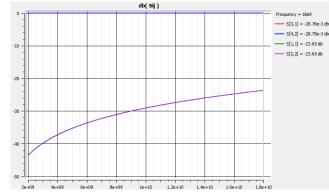

#### Ironwood\_Socket\_SGS\_07-09-2020.s4p

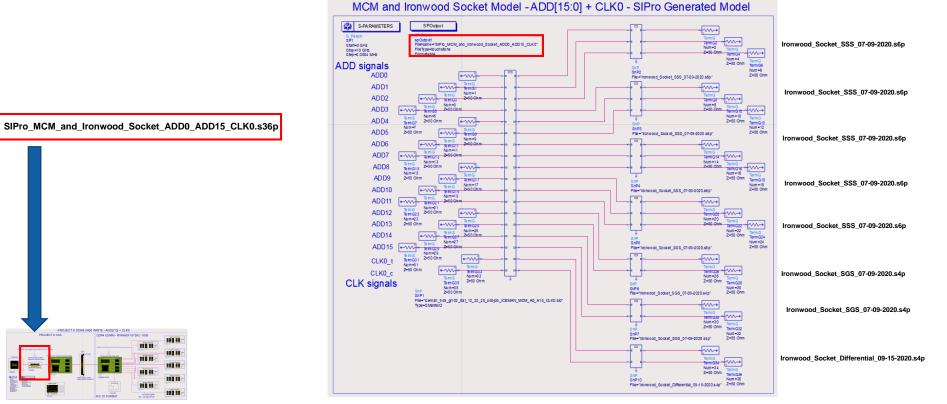

• 3 Ironwood Socket Models were used in combination with the respective MCM model for the Package Model

=>MCM model + Socket model = Package Model \*This is shown later

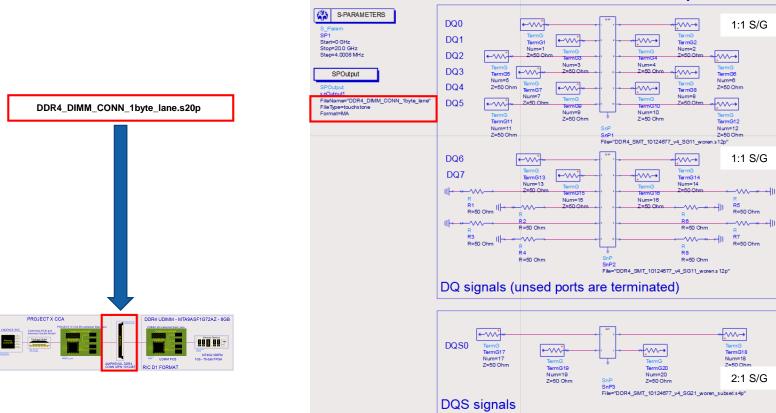

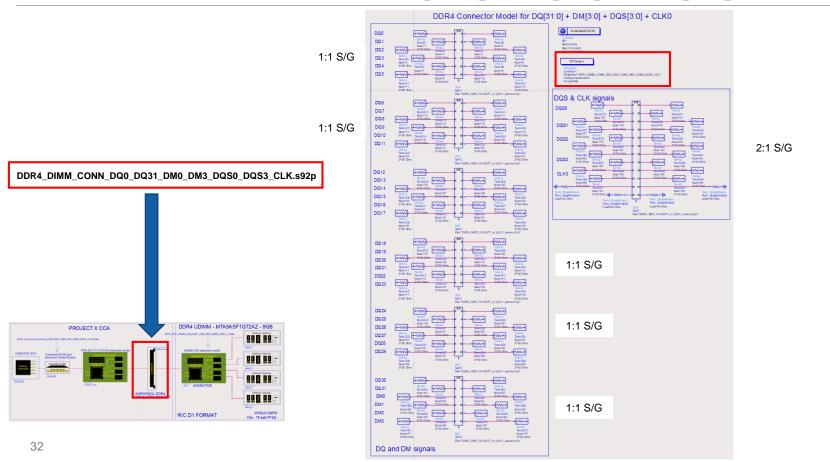

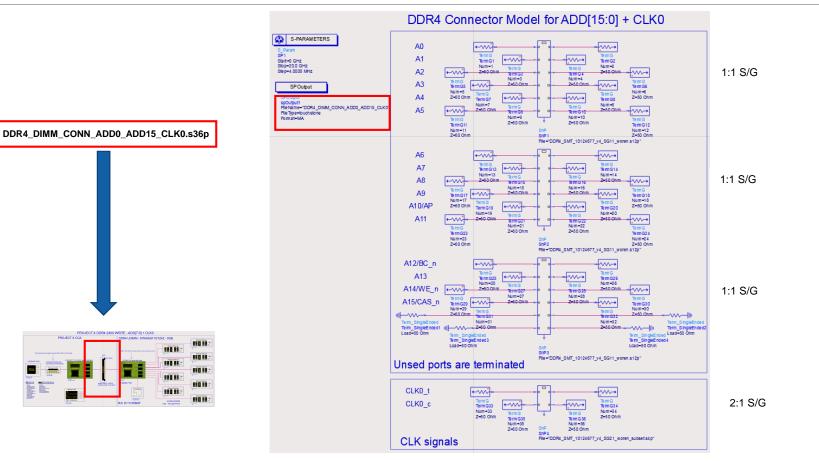

## System Models - DDR4 288-pin DIMM Connector Model

#### AMPHENOL MPN: 10124677

Model Name: SPa\_DDR4\_SMT\_10124677\_v4

DIMM Connector Model extracted from: SPa\_DDR4\_SMT\_10124677\_v4.zip

2 DIMM connector Models were used in combination to form a complete DIMM connector model

ATR

ETCH\_TOP

ETCH\_P\_2

ETCH\_S\_3

ETCH\_S\_5

ETCH\_S

ETCH\_P\_9

ETCH BOTTOM

POLYIMIDE (3.4)

FR-4 (4.2)

FR-4 (4.2)

0.08 millimeter

FR-4 (4.2) 0.08 millimeter

FR-4 (4.2)

FR-4 (4.2) 0.1 millimeter

ATR

0.1 millimeter FR-4 1 (4.5)

(0.015+0.045) millime...

FR-4 (4.2) (0.07+0.015) millimeter

(0.15+0.03) millimeter

(0.39+0.03) millimeter

(0.15+0.03) millimeter

FR-4 (4.2) (0.07+0.015) millimeter

POLYIMIDE (3.4) (0.015+0.045) millime...

DDR4 UDIMM - MTA9ASF1G72A7 - 8G

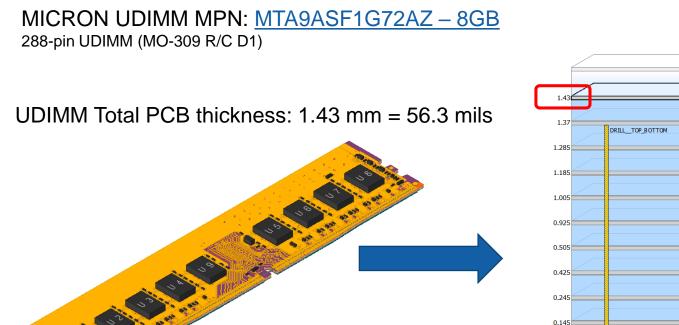

## System Models - UDIMM R/C D1 Model & PCB Stack-Up

SIPro Imported model

JEDEC UDIMM R/C D1 (imported DIMM)

10L Stack-up

0.06

0 millimete

#### 8

## System Models - UDIMM R/C D1 Model & PCB Stack-Up

JEDEC Standard No. 21C Page 4.20.26-27

#### 6.7 Reference Stackups

This section defines the preferred stackup for 6, 8, and 10 layer UDIMMs. Stackup for specific cards may be different from the preferred stackups in the tables below.

#### Table 15 — Preferred 10 Layer Stackup for UDIMMs

| ayers |             |        |         |                  |

|-------|-------------|--------|---------|------------------|

|       | Solder Mask | 15 µm  |         |                  |

| 1     | Cu          | 45 µm  | Signal  | 3/8 oz + Plating |

|       | Prepreg     | 70 µm  |         |                  |

| 2     | Cu          | 15 µm  | VDD/VSS | 1/2 oz           |

|       | Core        | 100 µm | •       |                  |

| 3     | Cu          | 15 µm  | Signal  | 1/2 oz           |

|       | Prepreg     | 150 µm |         |                  |

| 4     | Cu          | 15 µm  | VDD/VSS | 1/2 oz           |

|       | Core        | 80 µm  | -       |                  |

| 5     | Cu          | 15 µm  | Signal  | 1/2 oz           |

|       | Prepreg     | 390 µm |         |                  |

| 6     | Cu          | 15 µm  | Signal  | 1/2 oz           |

|       | Core        | 80 µm  |         |                  |

| 7     | Cu          | 15 µm  | VDD/VSS | 1/2 oz           |

|       | Prepreg     | 150 µm |         |                  |

| 8     | Cu          | 15 µm  | Signal  | 1/2 oz           |

|       | Core        | 100 µm |         |                  |

| 9     | Cu          | 15 µm  | VDD/VSS | 1/2 oz           |

|       | Prepreg     | 70 µm  | -       |                  |

| 10    | Cu          | 45 µm  | Signal  | 3/8 oz + Plating |

|       | Solder Mask | 15 µm  |         |                  |

Total Thickness: 1400 ± 100 µm as measured across connector contact fingers (without solder mask)

## UDIMM Total Model thickness

$= 1.43 \text{ mm} - \text{Solder mask} (0.015^{*}2) = 1.4 \text{ mm}$

=> Meets <u>JEDEC DDR4 SDRAM UDIMM Design</u> <u>Specification (Rev. 1.10 Aug 2015) for 10L stack-up:</u> 1400 um +/- 100 um

## System Models - IBIS Models – UDIMM MICRON SDRAM

#### MICRON SDRAM MPN: MT40A1G8

| z91b.ibs * IBIS 4.2 Model<br>  8Gb DDR4 SDRAM - Die Revision "A"<br>  This Model is valid for Commercial Temperature Range 0C<=Tc<=95C<br>                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Valid for DDR4-1600/1866/2133/2400/2666 operation<br>  Models *_2666 are applicable for speed grade 2666 Mbps (-075) and below                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Part Number VDD/VDDQ Architecture Package                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ,<br>MT40A2G4PM 1.2V/1.2V 2Gb x.4 78-Ball FBGA                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MT40A1G8PM       1.2V/1.2V       1Gb       x 8       78-Ball FBGA         MT40A512M16HA       1.2V/1.2V       512Mb x 16       96-Ball FBGA         MT40A2G4Z91B       1.2V/1.2V       2Gb       x 4       Bare Die         MT40A1G8Z91B       1.2V/1.2V       1Gb       x 8       Bare Die         MT40A512M16Z91B       1.2V/1.2V       1Gb       x 8       Bare Die         IMT40A512M16Z91B       1.2V/1.2V       512Mb x 16       Bare Die         [IBIS Ver]       4.2 | Model used for simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>[File Name] z91b.ibs</li> <li>[Date] 09/22/2014</li> <li>[File Rev] 1.0</li> <li>[Source] From silicon level SPICE model at Micron Technology, Inc.<br/>For support e-mail modelsupport@micron.com</li> </ul>                                                                                                                                                                                                                                                       | PROJECT X CCA<br>Province Toxic and the set of |

# DDR4-2400 DQ AND DQS ANALYSIS 1 Byte Lane (Write Only)

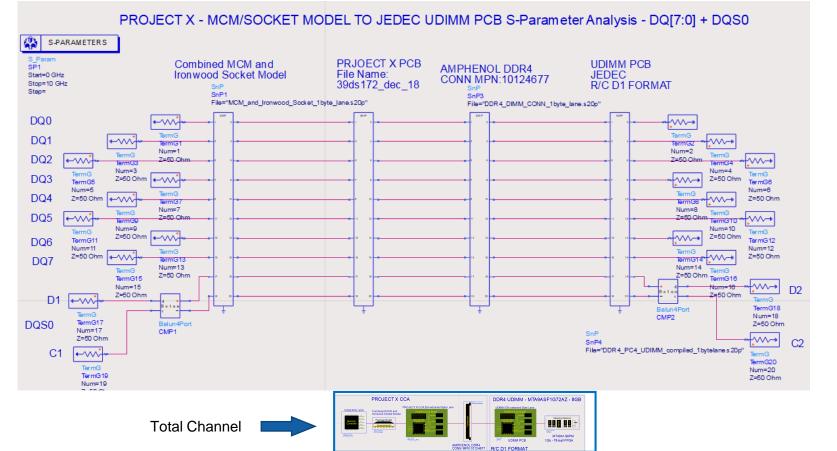

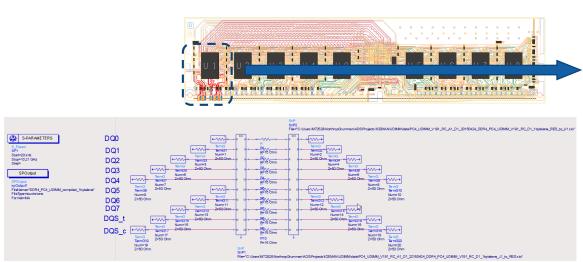

#### Total Channel S-Parameter Simulation Model – 1 byte Lane - DQ[7:0] + DQS0

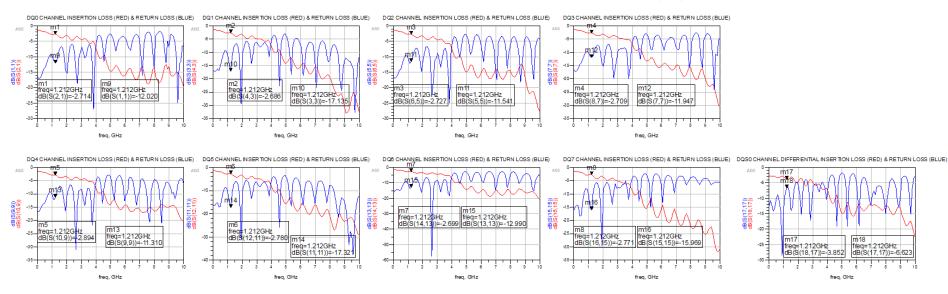

#### Total Channel S-parameter – 1 byte Lane - DQ[7:0] + DQS0 – Insertion Loss & Return Loss - Results

#### TOTAL CHANNEL - PROJECT X MCM to UDIMM INSERTION LOSS (RED) and RETURN LOSS (BLUE) - DQ[0:7] + DQS0

\*DQ <u>total</u> channel insertion loss = ~ (<u>-2.7 dB</u>) @ 1.2GHz \*Worst case insertion loss for DQ4 @ (-2.89 dB) @ 1.2GHz \*DQ <u>total</u> channel return loss = ~(<u>-11.5 dB</u>) @ 1.2GHz \*Worst case return loss for DQ4 @ (-11.3 dB) @ 1.2GHz

\*DQS0 <u>total</u> channel insertion loss = ~ (<u>-3.8 dB</u>) @ 1.2GHz \*DQS0 <u>total</u> channel return loss = ~ (<u>-6.6 dB</u>) @ 1.2GHz

### Simulation Model – DDR4-2400 Write – 1 byte Lane – DQ[7:0] + DQS0

#### Simulation Model – DDR4-2400 Write – with SIPro EM EXTRACTED MCM Model

| Memory Designer Setup             |

|-----------------------------------|

| MD_Setup                          |

| MD_Setup                          |

| dramType=DDR4                     |

| dataCycle=Write                   |

| · dataCycleMode=Continuous· · · · |

| .caCtrlTiming=1T                  |

| speedGrade=2400                   |

| UseCustomSpeedGrade=0             |

| Custom SpeedGrade=1000            |

|                                   |

|                                   |

| DDR Sim 1 1 1 1 1 1               |

|                                   |

| DDRSim                            |

| DDRSim1                           |

| AntiAliasingWindow=1              |

| EnforcePassivity=yes              |

| EnforceStrictPassivity=           |

| ImpMaxFreq=                       |

| LowBERFloor=yes                   |

| MaxImpulseLength=100              |

| Mode=Statistical                  |

| NumberTimePtPerUI=32              |

| SaveToDataset=                    |

| StatusLevel=2                     |

| ToleranceMode=Auto                |

| NumberOfBits=100                  |

| BlockSize=1024                    |

# DDR4 MCM + Socket Model – 1 byte lane

MCM and Ironwood Socket 1byte lane.s20p

DDR4 Connector Model for 1-byte lane

# **DDR4 DIMM Connector Model – 1 byte lane**

## UDIMM EM Extracted Model – 1 byte lane – DQ[7:0] + DQS0

ADS 2020 – prevented complete EM extraction model with in-line component – this is resolved in ADS 2021. => This model consist is two compiled models.

EM Extraction based on UDIMM Layout Data: PC4-UDIMM\_V191\_RC\_A1\_D1\_20150424.zip

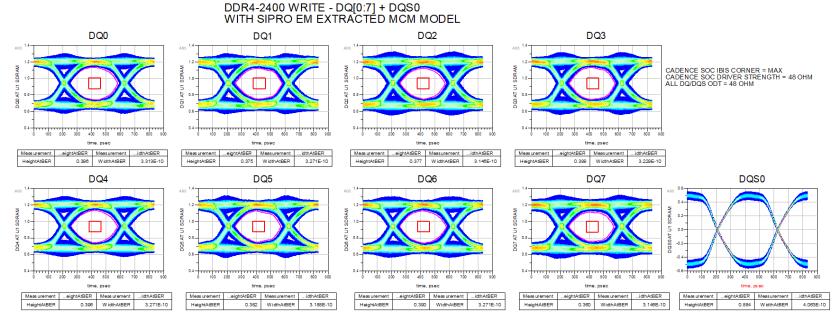

#### DDR4-2400 Write – DQ[7:0] + DQS0 – Results – No Random Jitter Added

#### Probe Point

\*DQ eye mask shown is for JEDEC DDR4-2400 to achieve BER 1E-16. \*Results shown are for ODT =  $48\Omega$  on all DQ signals.

All signals pass Eye mask compliance for DDR4-2400

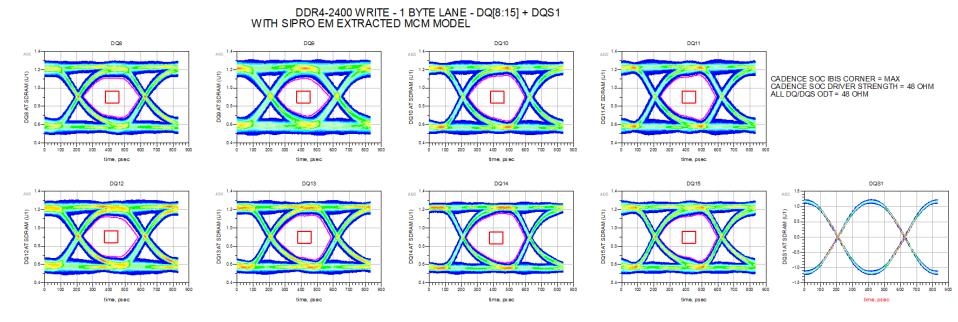

### DDR4-2400 Write – DQ[15:8] + DQS1 – Results – No Random Jitter Added

#### Probe Point

DDR4 UDIMM - MTA9ASE1G72AZ - 8GB

UDMM PCF

AMPHENOL DDR4 CONN MPN: 10124877 R/C D1 FORMAT \*DQ eye mask shown is for JEDEC DDR4-2400 to achieve BER 1E-16. EM Extraction based on PROJECT X Layout Data: projectx\_39ds172\_dec-18.tgz

All signals pass Eye mask compliance for DDR4-2400

PROJECT X CCA

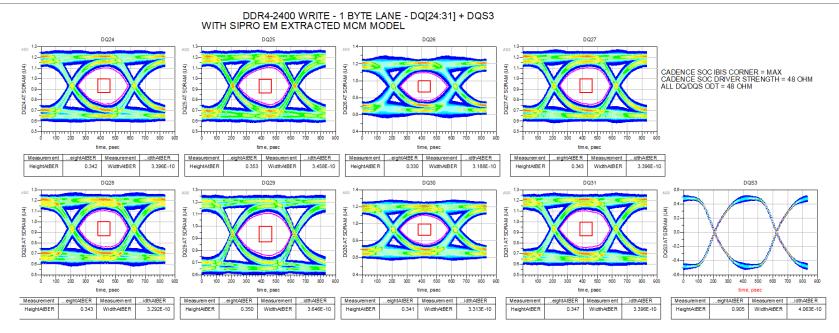

#### DDR4-2400 Write – DQ[31:24] + DQS3 – Results – No Random Jitter Added

#### Probe Point

EM Extraction based on PROJECT X Layout Data: projectx\_39ds172\_dec-18.tgz \*DQ eye mask shown is for JEDEC DDR4-2400 to achieve BER 1E-16.

All signals pass Eye mask compliance for DDR4-2400

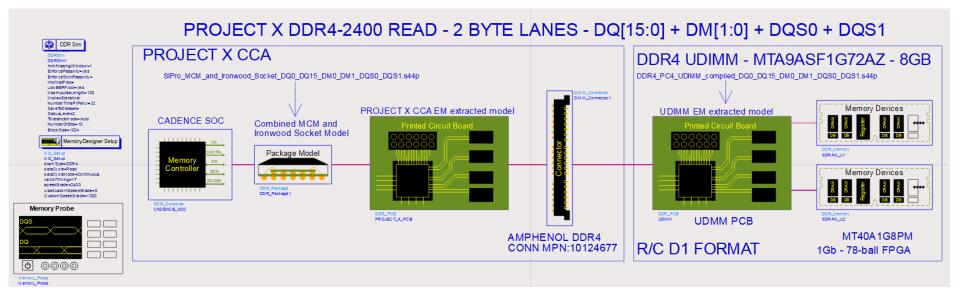

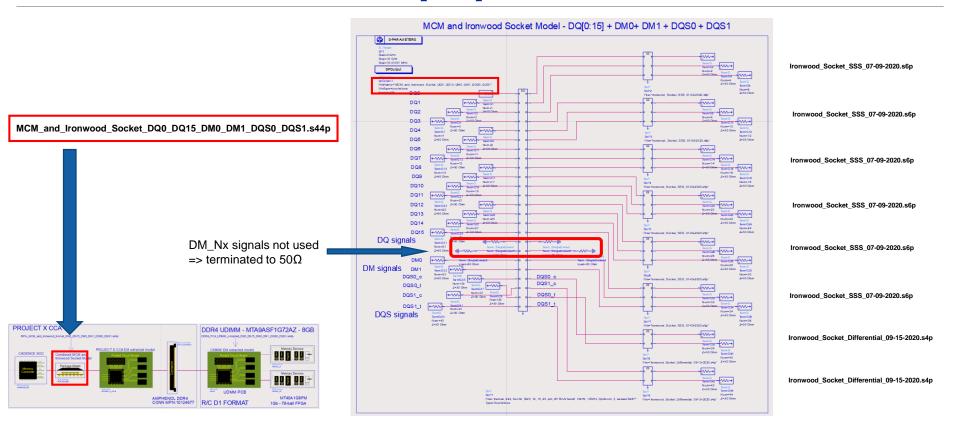

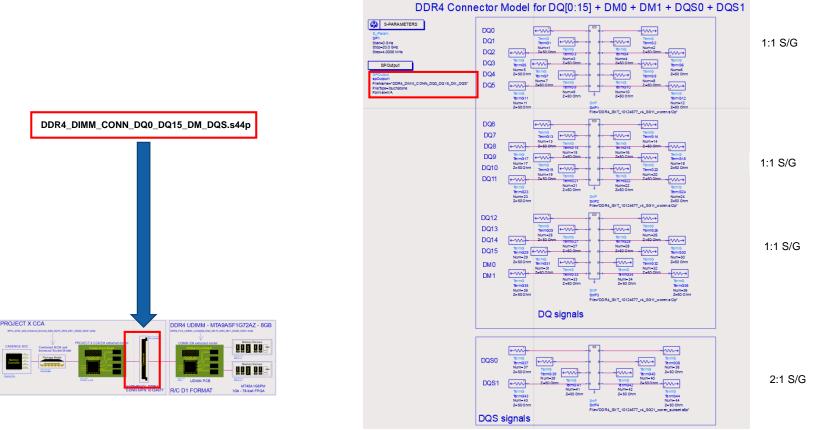

# DDR4-2400 DQ[15:0] + DM[1:0] + DQS0 + DQS1 READ AND WRITE ANALYSIS

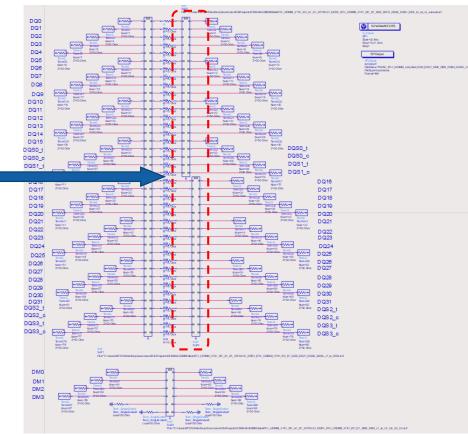

#### Simulation Model – DDR4-2400 Write/Read – DQ[15:0] + DM[1:0] + DQS0 + DQS1

#### DDR4 MCM + Socket Model – DQ[15:0]+DM0+DM1+DQS0+DQS1

## DDR4 DIMM Connector Model – DQ[15:0] + DM[1:0] + DQS0 + DQS1

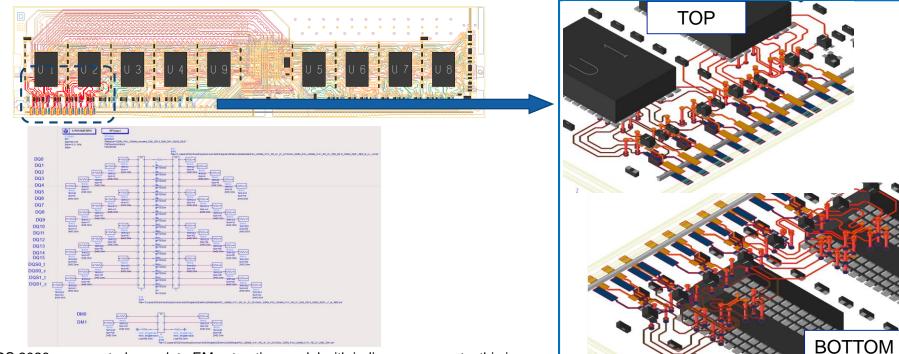

### UDIMM EM Extracted Model – DQ[15:0]+DM0+DM1+DQS0+DQS1

ADS 2020 – prevented complete EM extraction model with in-line component – this is resolved in ADS 2021. => This model consist is two compiled models.

EM Extraction based on UDIMM Layout Data: PC4-UDIMM\_V191\_RC\_A1\_D1\_20150424.zip

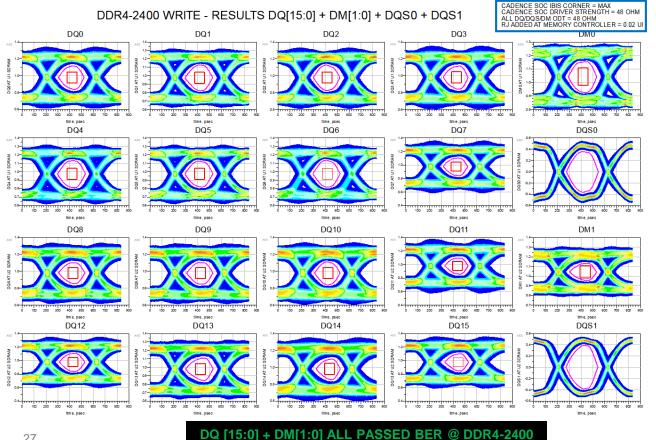

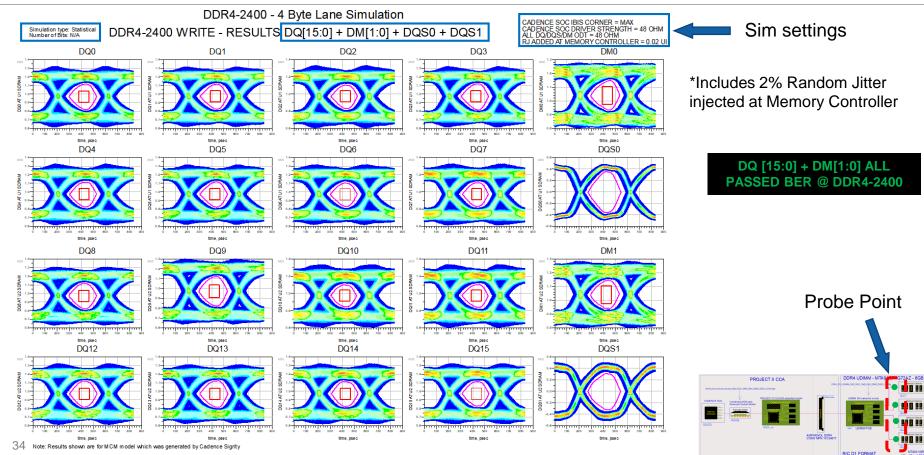

## DDR4-2400 Write – 2 byte lane Results – DQ[15:0] + DM[1:0] + DQS0 + DQS1

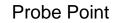

Sim settings

\*Includes 2% Random Jitter injected at Memory Controller

### DDR4-2400 Read – 2 byte lane Results – DQ[15:0] + DM[1:0] + DQS0 + DQS1

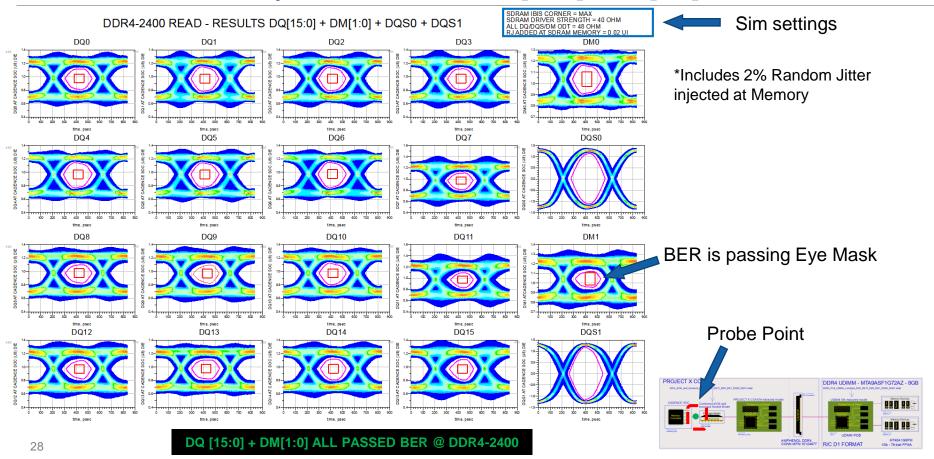

## Simulation Model – DDR4-2400 Write – DQ[31:0] + DM[3:0] + DQS[3:0]

PROJECT X DDR4-2400 WRITE - 4 BYTE LANES - DQ[31:0] + DM[3:0] + DQS3 + DQS2 + DQS1 + DQS0

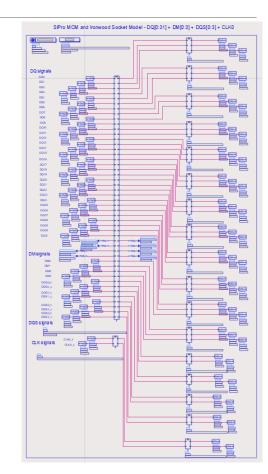

# DDR4 MCM + Socket Model – 4 byte lanes

Due to memory limitation on local machine in SIPro, a single 4 byte lane MCM model was not able to be extracted.

=> Cadence Sigrity MCM extracted model was used for MCM in the combined MCM + Socket model

#### DDR4 DIMM Connector Model – DQ[31:0] + DM[3:0] + DQS[3:0]

## UDIMM EM Extracted Model – DQ[31:0] + DM[3:0] + DQS[3:0]

EM Extraction based on UDIMM Layout Data: PC4-UDIMM\_V191\_RC\_A1\_D1\_20150424.zip

In SIPro, EM extraction would output incorrect results for random DQ nets. The solution was to break up the extraction from 4 byte lanes into 2 byte lanes. This could have been a convergence issue in SIPro with ADS 2020U1.

\*ADS 2020 – prevented complete EM extraction model with in-line component – this is resolved in ADS 2021. => This model consist is two compiled models.

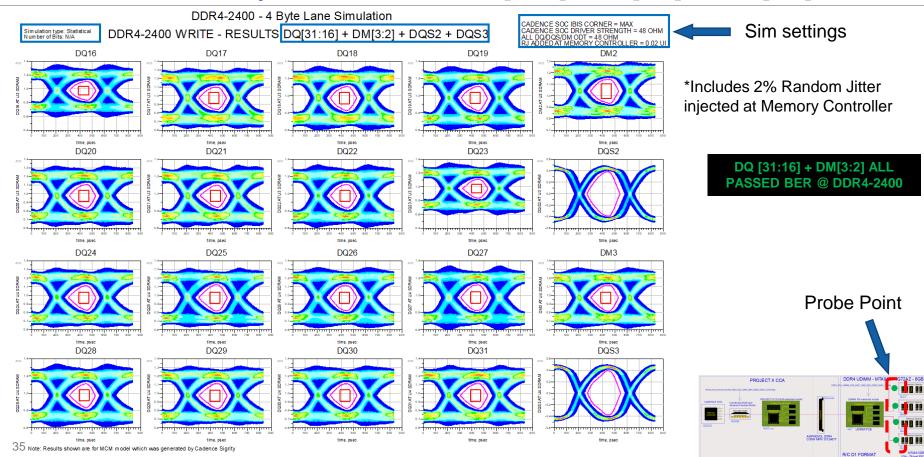

## DDR4-2400 Write – 4 byte lane Results – DQ[31:0] + DM[3:0] + DQS[3:0]

## DDR4-2400 Write – 4 byte lane Results – DQ[31:0] + DM[3:0] + DQS[3:0]

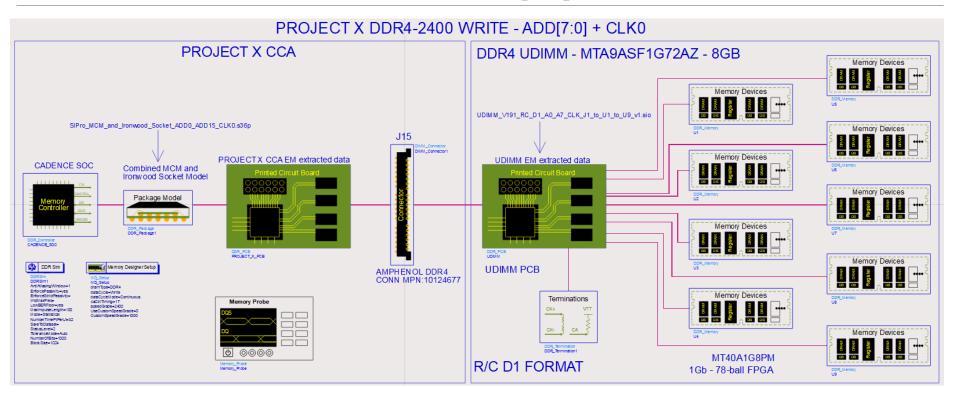

# DDR4-2400 Write ADD[7:0] + CLK0 Results with UDIMM (R/C D1)

## Simulation Model – DDR4-2400 Write – ADD[7:0] + CLK0

### DDR4 Memory Controller Package Delay Settings - ADD[7:0] + CLK0

| Select IBIS/ EBD File C:/Users/M72528/NorthropGrumman/ADS/Projects/DDR4_wrk/data/gf_12lp_ddr4_EDITED_1v2.ibs | Browse | View |

|--------------------------------------------------------------------------------------------------------------|--------|------|

| Component DDR4                                                                                               |        |      |

| Assign signal property by: IBIS Signal Name 🔻 🗌 Enable Channel ID Matching 🛛 Collapse Power Node             |        |      |

| Use Delay File                                                                                               | Browse | View |

| Enable DBI 🔿 DBIdc 🕥 DBIac 🔘 None                                                                            |        |      |

Assign Signal Property and Enable Pins for Simulation

| Re         | eference Designator and IBI | IS Table         |             |              | Signal Property Table |             |            |   |

|------------|-----------------------------|------------------|-------------|--------------|-----------------------|-------------|------------|---|

| Search     | Search                      | Search           | Search      | Search       | Y                     | Search      | Search     |   |

| Ref Des    | IBIS Pin Name               | IBIS Signal Name | Signal Type | Signal Index | Simulate              | Delay (sec) | Channel ID | ^ |

| U8_ADS_DIE | 48                          | ADD0             | А           | 0            | Υ                     | 115e-12     | 0          |   |

| U8_ADS_DIE | 49                          | ADD1             | А           | 1            | γ                     | 96e-12      | 0          |   |

| U8_ADS_DIE | 50                          | ADD2             | А           | 2            | γ                     | 105.6e-12   | 0          |   |

| U8_ADS_DIE | 51                          | ADD3             | А           | 3            | γ                     | 100.7e-12   | 0          |   |

| U8_ADS_DIE | 52                          | ADD4             | А           | 4            | γ                     | 111.6e-12   | 0          |   |

| U8_ADS_DIE | 53                          | ADD5             | А           | 5            | γ                     | 118.8e-12   | 0          |   |

| U8_ADS_DIE | 54                          | ADD6             | А           | 6            | γ                     | 122.6e-12   | 0          |   |

| U8_ADS_DIE | 55                          | ADD7             | А           | 7            | γ                     | 124.4e-12   | 0          |   |

| U8_ADS_DIE | 65                          | CLKN0            | CK_c        | 0            | γ                     | 99.6e-12    | 0          |   |

| U8_ADS_DIE | 64                          | CLKP0            | CK_t        | 0            | Υ                     | 98.9e-12    | 0          |   |

|            |                             |                  |             |              |                       |             |            | ~ |

# DDR4 MCM + Socket Model – ADD[15:0] + CLK0

MCM Model: projectX\_MCM\_A0\_A15\_CLK0.sio

# DDR4 DIMM Connector Model – ADD[15:0] + CLK0

# UDIMM EM Extracted Model – ADD[7:0] + CLK0

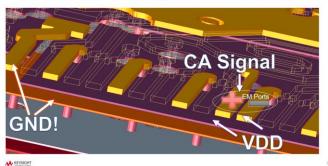

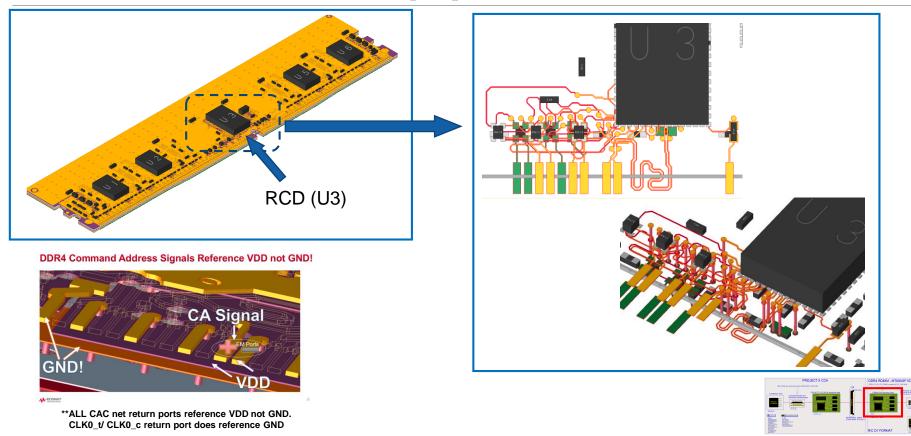

\*\*Important Note: All CAC nets & CLK0 had return port set to VDD on UDIMM.

#### DDR4 Command Address Signals Reference VDD not GND!

EM Extraction based on UDIMM Layout Data: PC4-UDIMM\_V191\_RC\_A1\_D1\_20150424.zip

## DDR4 ADD & CLK Termination Settings – ADD[7:0] + CLK0

| Termination for CA and                    | Control Signals |                  |                    |                        |          |   |

|-------------------------------------------|-----------------|------------------|--------------------|------------------------|----------|---|

| VTT (Volts) 0.6                           |                 | R_CA (Ohms) 39.0 |                    | Rs_Control (Ohms) 39.0 |          | _ |

| Termination for Clock Sig                 | gnals           |                  |                    |                        |          |   |

| O Termination Topolog                     |                 |                  |                    |                        |          |   |

| R_CK_diff (Ohms)                          |                 |                  |                    |                        |          |   |

| C Termination Topolog<br>R_CK_SE (Ohms) 5 |                 |                  | VTT_CK (Volts) 1.0 |                        |          |   |

| Termination Topolog                       |                 |                  | VII_CR (Volts) 1.0 |                        |          |   |

| R_CK_SE (Ohms)                            |                 | C_CK (pFs) 10    |                    | VTT_CK (Volts) 0.6     |          | _ |

| Search                                    | Search          | Search           | Search             | Search                 | k        | _ |

| Port Name                                 | RefDes          | Signal Type      | Signal Index       | Channel ID             | Simulate |   |

| CLK0_B_RN47                               | RN47            | CK_c             | 0                  | 0                      | Y        | _ |

| CLK0_RN47                                 | RN47            | CK_t             | 0                  | 0                      | Y        |   |

| A7_RN51                                   | RN51            | А                | 7                  | 0                      | Y        |   |

| A6_RN49                                   | RN49            | А                | 6                  | 0                      | Y        |   |

| A5_RN53                                   | RN53            | А                | 5                  | 0                      | Y        |   |

| A4_RN53                                   | RN53            | Α                | 4                  | 0                      | Y        |   |

| A3_RN53                                   | RN53            | A                | 3                  | 0                      | Y        |   |

| A2_RN51                                   | RN51            | А                | 2                  | 0                      | Y        |   |

| A1_RN49                                   | RN49            | A                | 1                  | 0                      | Y        |   |

| A0_RN49                                   | RN49            | A                | 0                  | 0                      | Y        |   |

|                                           |                 |                  |                    |                        |          |   |

|                                           |                 |                  |                    |                        |          |   |

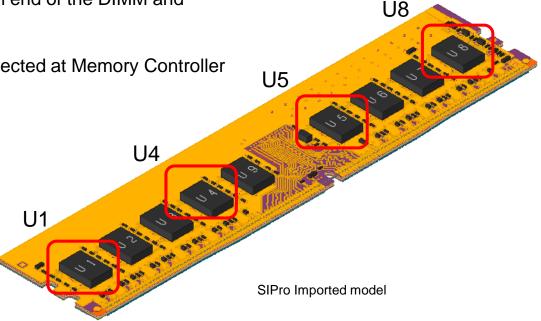

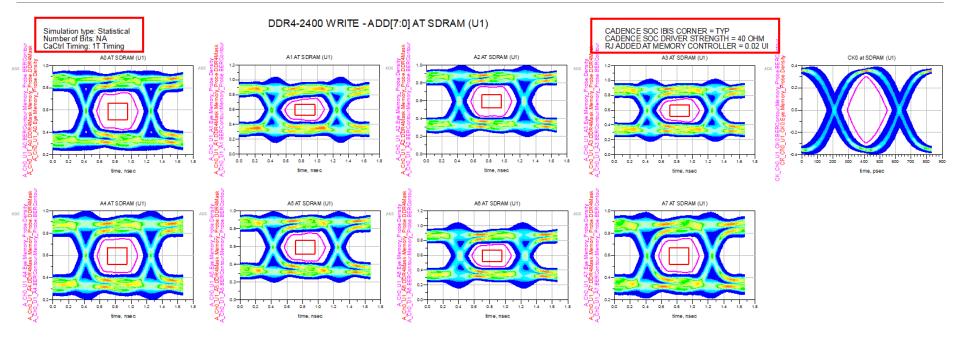

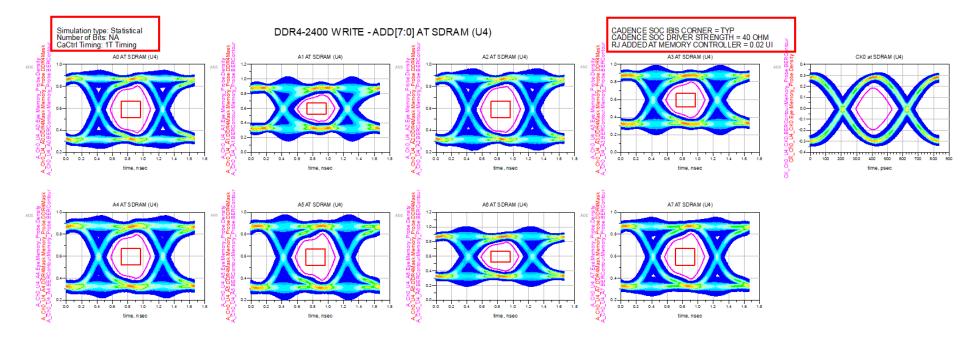

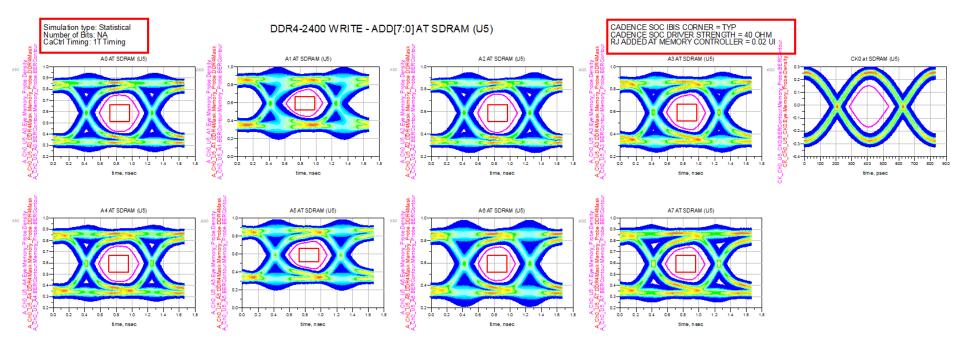

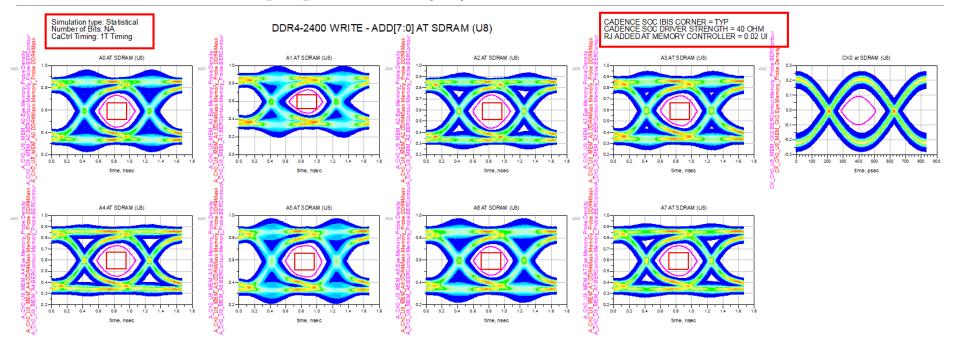

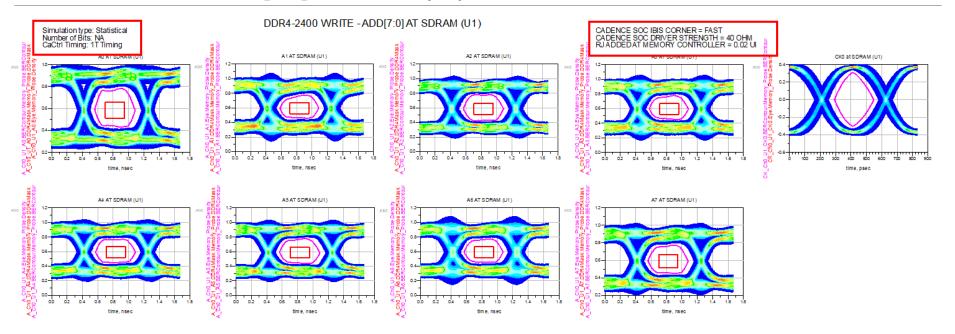

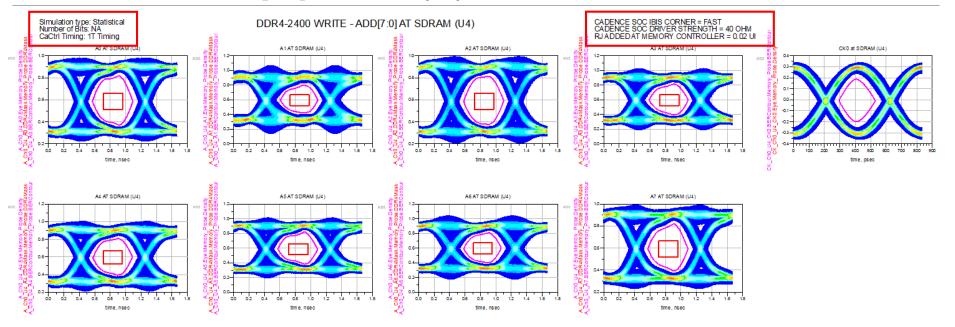

# **ADDRESS Signal SI Analysis on UDIMM**

MICRON UDIMM MPN: MTA9ASF1G72AZ – 8GB 288-pin UDIMM (MO-309 R/C D1)

- Analysis shown will only include analysis at the following SDRAMs at the UDIMM for A[7:0] + CLK0 due to fly-by topology on UDIMM for CAC nets

- This allows analysis to be done at each end of the DIMM and middle points on DIMM

- Results shown include 2% Random Jitter injected at Memory Controller with BER = 1E-16

### Results DDR4-2400 ADD[7:0] at SDRAM (U1) on UDIMM – TYP IBIS Corner

44

### Results DDR4-2400 ADD[7:0] at SDRAM (U4) on UDIMM – TYP IBIS Corner

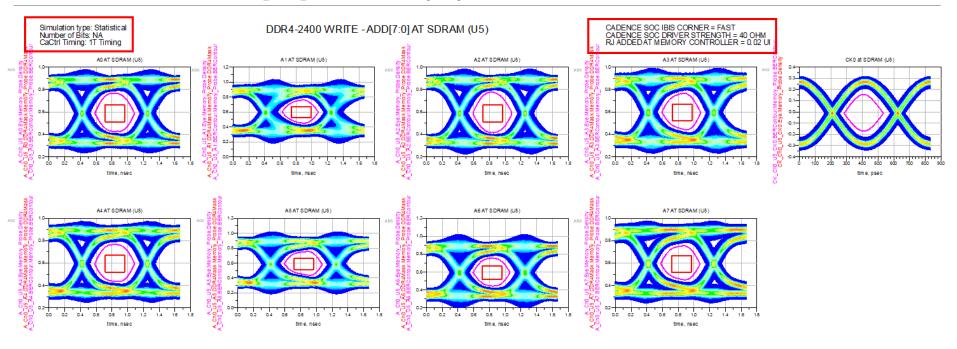

### Results DDR4-2400 ADD[7:0] at SDRAM (U5) on UDIMM – TYP IBIS Corner

46

### Results DDR4-2400 ADD[7:0] at SDRAM (U8) on UDIMM – TYP IBIS Corner

47

### Results DDR4-2400 ADD[7:0] at SDRAM (U1) on UDIMM – FAST IBIS Corner

### Results DDR4-2400 ADD[7:0] at SDRAM (U4) on UDIMM – FAST IBIS Corner

49

### Results DDR4-2400 ADD[7:0] at SDRAM (U5) on UDIMM – FAST IBIS Corner

### Results DDR4-2400 ADD[7:0] at SDRAM (U8) on UDIMM – FAST IBIS Corner

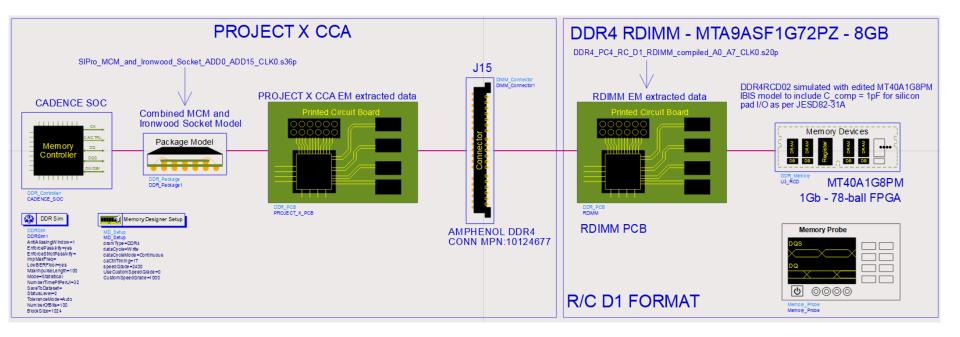

# DDR4-2400 Write ADD[7:0] + CLK0 Results with RDIMM (R/C D1)

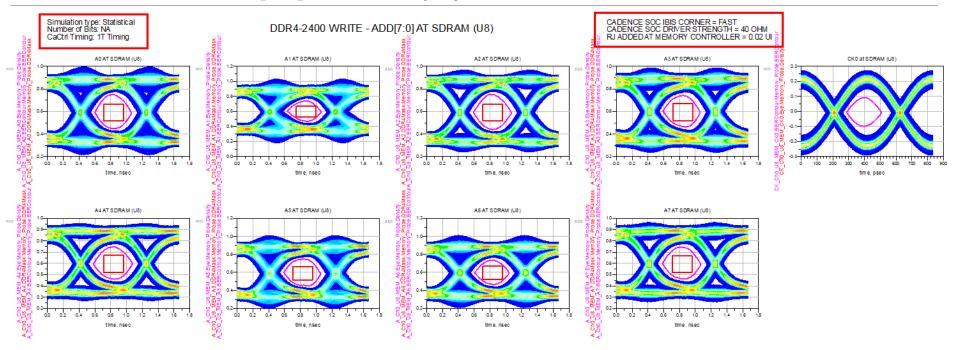

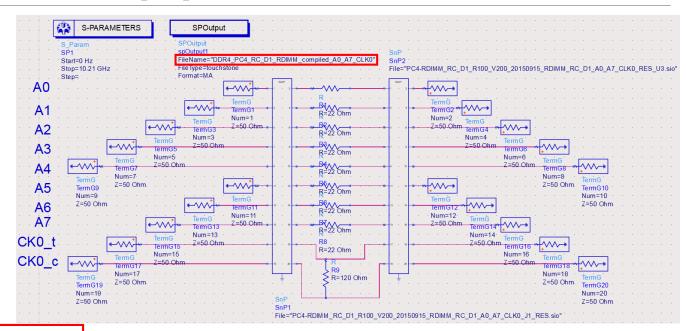

## Simulation Model – DDR4-2400 Write – ADD[7:0] + CLK0 with RDIMM

# System Models - IBIS Models - RDIMM RCD

### MICRON SDRAM MPN: MT40A1G8

z91b.ibs \* IBIS 4.2 Model 8Gb DDR4 SDRAM - Die Revision "A" This Model is valid for Commercial Temperature Range 0C<=Tc<=95C

Valid for DDR4-1600/1866/2133/2400/2666 operation Models \*\_2666 are applicable for speed grade 2666 Mbps (-075) and below

Part Number VDD/VDDQ Architecture Package

78-Ball FBGA MT40A2G4PM  $12V/12V/2Gh \times 4$ MT40A1G8PM 1.2V/1.2V 1Gb x 8 78-Ball FBGA MT40A512M16HA 1.2V/1.2V 96-Ball FBGA 512Mb x 16 MT40A2G4Z91B 1.2V/1.2V 2Gb x 4 Bare Die 1.2V/1.2V 1Gb x 8 MT40A1G8Z91B Bare Die MT40A512M16Z91B 1.2V/1.2V 512Mb x 16 Bare Die [IBIS Ver] 4.2 [File Name] z91b.ibs 09/22/2014 [Date] [File Rev] 1.0 From silicon level SPICE model at Micron Technology, Inc. [Source]

For support e-mail modelsupport@micron.com

MICRON SDRAM ibis model (z91b.ibs) was edited by setting the C\_comp = 1pF as per the min, typ, & max allowed input/output pad capacitance for CAC and CLK pins, this is defined in the JEDEC JESD82-31A standard, Table 139

Model used for simulation

-----------

## **RDIMM EM Extracted Model – ADD[7:0] + CLK0**

EM Extraction based on UDIMM Layout Data: PC4-RDIMM\_RC\_D1\_R100\_V200\_20160408.zip

## **RDIMM EM Extracted Model – ADD[7:0] + CLK0**

\*All CAC nets shown include ideal 22Ω series resistors model to RCD \*CLK0 include ideal 120Ω termination added in this model to RCD

EM Extraction based on UDIMM Layout Data: PC4-RDIMM\_RC\_D1\_R100\_V200\_20160408.zip

DDR4\_PC4\_RC\_D1\_RDIMM\_compiled\_A0\_A7\_CLK0.s20p

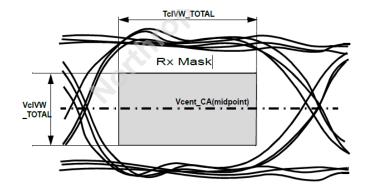

# **RDIMM Receiver Eye Mask at Registered Clock Driver (RCD)**

Figure 39 - CA Receiver(Rx) mask

DDR4RCD02 input receiver to successfully capture a valid input signal with BER < 1e-18

\*Table 109 is from JEDEC JESD82-31A

| Speed                                                                                                                                                |                                                                                                                                                                                                                                        | DDR4-1600/<br>1866/2133 DDR4-2400                                                                |                                                                                              | -2400                                                                          | DDR4-2666                                                                         |                                                                                | DDR4-2933                                           |                                                 | DDR4-3200                            |                   | Unit                                  | NOTE                  |                |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------|--------------------------------------|-------------------|---------------------------------------|-----------------------|----------------|

| Symbol                                                                                                                                               | Parameter                                                                                                                                                                                                                              | Min                                                                                              | Мах                                                                                          | Min                                                                            | Мах                                                                               | Min                                                                            | Мах                                                 | Min                                             | Max                                  | Min               | Max                                   |                       |                |

| VcIVW_TOTAL                                                                                                                                          | Rx Mask p-p<br>voltage total                                                                                                                                                                                                           | -                                                                                                | 150                                                                                          | -                                                                              | 120                                                                               | -                                                                              | 120                                                 | -                                               | 110                                  | -                 | 100                                   | mV                    | 1,2,3,         |

| TcIVW_TOTAL                                                                                                                                          | Rx timing window total                                                                                                                                                                                                                 | -                                                                                                | 0.2                                                                                          | -                                                                              | 0.15                                                                              | -                                                                              | 0.15                                                | -                                               | 0.135                                | -                 | 0.135                                 | UI                    | 1,4            |

| VIHL_AC                                                                                                                                              | CAAC input pulse<br>amplitude pk-pk                                                                                                                                                                                                    | 180                                                                                              | -                                                                                            | 150                                                                            | -                                                                                 | 140                                                                            | -                                                   | 130                                             | -                                    | 120               | -                                     | mV                    | 5              |

| TcIPW                                                                                                                                                | CA input pulse<br>width                                                                                                                                                                                                                | 0.5                                                                                              | -                                                                                            | 0.4                                                                            | -                                                                                 | 0.3                                                                            | -                                                   | 0.3                                             | -                                    | 0.3               | -                                     | UI                    | 6              |

| tCK2CA                                                                                                                                               | CK to CA offset                                                                                                                                                                                                                        | -0.1                                                                                             | 0.1                                                                                          | -0.1                                                                           | 0.1                                                                               | -0.1                                                                           | 0.1                                                 | -0.1                                            | 0.1                                  | -0.1              | 0.1                                   | UI                    | 7              |

| tCACA                                                                                                                                                | CA to CA offset                                                                                                                                                                                                                        | -                                                                                                | 0.04                                                                                         | -                                                                              | 0.04                                                                              | -                                                                              | 0.04                                                | -                                               | 0.04                                 | -                 | 0.04                                  | UI                    | 8              |

| SRIN_cIVW                                                                                                                                            | Input Slew Rate<br>over<br>VcIVW_TOTAL                                                                                                                                                                                                 | 1                                                                                                | 5                                                                                            | 1                                                                              | 5                                                                                 | 1                                                                              | 5                                                   | 1                                               | 5                                    | 1                 | 5                                     | V/ns                  | 9              |

| mask is applied p<br>NOTE 2: Rx mas<br>Vcent_CA(midpo<br>NOTE 3: The Vcl<br>NOTE 4: Overshi<br>NOTE 5: CA inpu<br>any UI during wh<br>Vcent_CA(midpo | mask voltage and timi<br>ver bit and includes vo<br>k voltage AC swing p<br>int) and at least half o<br>VW voltage levels arr<br>oot and Undershoot S<br>to pulse signal swing i<br>ich there is a signal tr<br>int), which is defined | oltage ar<br>eak-pea<br>of VcIVW<br>e center<br>of center<br>of the ro<br>ansition.<br>in Figure | nd temper<br>k require<br>/_TOTAL<br>ed aroun<br>tions see<br>eceiver n<br>No timir<br>e 40. | erature d<br>ement ov<br>L(max) b<br>d Vcent<br>e Table<br>nust me<br>ng requi | Irift term<br>ver TcIV<br>below Vo<br>_CA(mid<br>117 and<br>et or exc<br>rement a | s. The d<br>W_TOT/<br>cent_CA<br>dpoint).<br>Figure 5<br>ceed VIH<br>above lev | esign sp<br>AL with a<br>(midpoin<br>50.<br>L_AC fo | ecification<br>at least f<br>nt).<br>or at leas | on is BEI<br>half of Vo<br>t one poi | R ≤1e-1<br>NVW_TO | 8. <del></del><br>OTAL(ma<br>the dura | ax) abov<br>tion of T | re<br>TcIPW fo |

| NOTE 7: CK to C<br>and temperature<br>NOTE 8: CA to C<br>for a given comp                                                                            | imum input pulse wid<br>A offset defined withir<br>variation.<br>A offset is defined as<br>onent. Includes all DD<br>ew rate over VcIVW N                                                                                              | the mag                                                                                          | D/CMD a<br>gnitude o<br>02 volta                                                             | nd CTR                                                                         | L inputs<br>ference<br>emperat                                                    | at DDR<br>betweer<br>ture varia                                                | n the min<br>ation.                                 | n and ma                                        | ax CK to                             | CA offse          | et at DD                              | R4RCD                 | 02 balls       |

#### Table 109 — CA Input Receiver Voltage Margin and AC Timing by Speed Bin for DDR4-1600 -3200

R/C D1 FORMAT

# DDR4-2400 Write Results – A[7:0] + CLK0 on RDIMM – MAX IBIS Corner

R/C D1 FORMAT

# DDR4-2400 Write Results – A[7:0] + CLK0 on RDIMM – SLOW IBIS Corner

# NORTHROP GRUMMAN