## Welcome to DESIGNCON® 2024 WHERE THE CHIP MEETS THE BOARD

Conference

January 30 – February 1, 2024

Santa Clara Convention Center

Expo

January 31 – February 1, 2024

JAN. 30 – FEB. 1, 2024

## Unmasking Voltage Regulator Instability: What Vendor Reference Designs Aren't Telling You

Speaker: Will McCaffrey, Northrop Grumman

Authors: Will McCaffrey, Northrop Grumman, Benjamin Dannan, Signal Edge Solutions

#### **Author Bios**

#### William McCaffrey

*Digital Hardware Engineer, Northrop Grumman* William.McCaffrey@ngc.com

Will McCaffrey is a Digital Hardware Engineer at Northrop Grumman Mission Systems. He holds a BSEE from Rochester Institute of Technology in Rochester NY, and a MSEE from Johns Hopkins University. His interest is in high-speed digital design, SI/PI simulation and measurement. He has authored peer-reviewed journal publications to Signal Integrity Journal and has co-authored a peer-reviewed publication to DesignCon 2022.

#### **Benjamin Dannan**

Chief Technologist, Signal Edge Solutions ben@signaledgesolutions.com

Benjamin holds a certification in cybersecurity, has a BSEE from Purdue University, a Master of Engineering in Electrical Engineering from The Pennsylvania State University, and graduated from the USAF Undergraduate Combat Systems Officer training school with an aeronautical rating. Benjamin is a trained Electronic Warfare Officer in the USAF with deployments on the EC-130J Commando Solo in Afghanistan and Iraq totaling 47 combat missions, as well as a trained USAF Cyber Operations Officer. In addition, he has co-authored multiple peer-reviewed journal publications and has received the prestigious DesignCon 2020 best paper award, given to authors leading as practitioners in semiconductor and electronic design.

JAN. 30 - FEB. 1, 2024

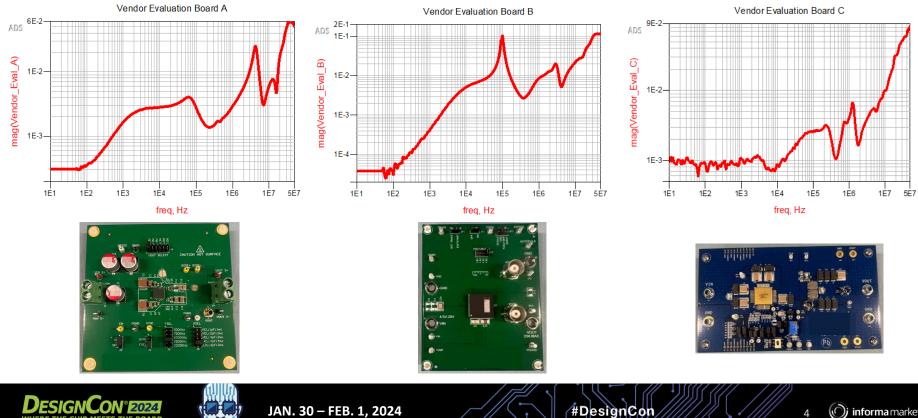

#### What Do All of These VRM Eval Boards Have in Common?

#### **They are ALL Unstable!**

| Eval Board<br>Regulator | Resonance<br>Frequency | Q Factor | Phase Margin      |

|-------------------------|------------------------|----------|-------------------|

| ISL70002SEHD            | 4.46 MHz               | 3.21     | 17.7 <sup>0</sup> |

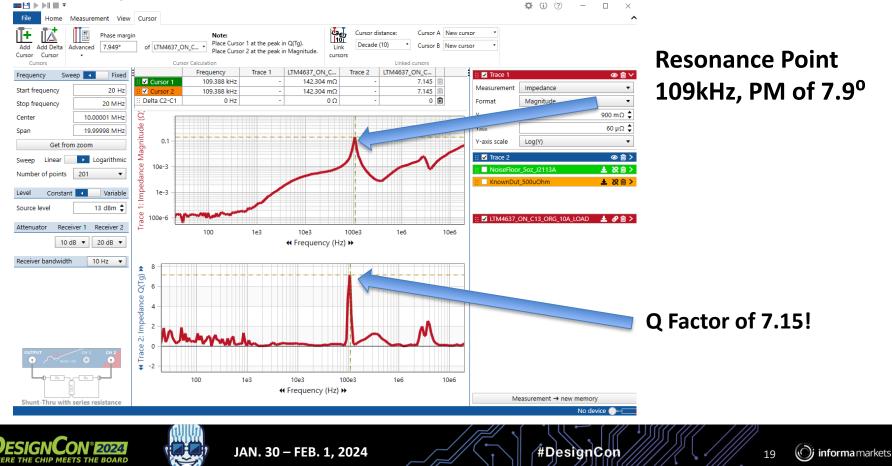

| LTM4637                 | 109 kHz                | 7.15     | 7.9 <sup>0</sup>  |

| TPSM843B22              | 1.44 MHz               | 3        | 19 <sup>0</sup>   |

#### Q < 2 is always 30° of phase margin!

#DesignCon

JAN. 30 - FEB. 1, 2024

5 🔘

#### What Makes These Regulators Unstable?

- There are resonances in the output impedance on the PDN

- A Bode Plot of the plant will show if you regulator is stable or not, but it will not tell you if you PDN is stable!

#### Definition of Target Impedance

- Voltage allowed set by the load

- o Imax set by the load, and the current is both dynamic and frequency independent

- Impedance is the only term the designer has control over! A poorly placed resonance could be devastating

$$Z_{Target} = \frac{\Delta V_{Allowed}}{\Delta I_{Max}}$$

#DesignCon

(i) informa markets

JAN. 30 - FEB. 1, 2024

#### **How Do We Measure Stability**

Stability is the most essential measurement to ensure closed loop performance

$$Closed \ Loop = \frac{Open \ Loop}{1+T}$$

#### Historically stability was measured through Bode plots

${\scriptstyle \circ}$  Requires injecting a signal into the loop

o Does not consider the PDN impact in stability assessment

JAN. 30 - FEB. 1, 2024

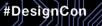

# What if we don't have access to the feedback network?

- To measure stability with a bode plot, we need to cut traces and inject a signal

- Sometimes all you have is a capacitor pad on the output voltage rail

- That is all you need!

Source: https://www.picotest.com/wemeasurepower2012/28-slide.html

#DesignCor

JAN. 30 - FEB. 1, 2024

## How do we practically measure NISM?

- Impedance Measurement provides three data points

- Impedance Magnitude, Phase, Group Delay

- o NISM takes it from there!

- NISM shows the systems stability, measures overall PDN

- NISM is available on all VNA and FRAs

- o Omicron Bode 100

- o Keysight E5061B

- o And many more!

Source: Picotest.com

#DesignCon

JAN. 30 – FEB. 1, 2024

(i) informa markets

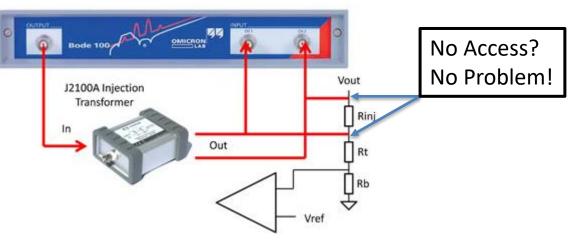

### Wanted: Flat Impedance and Low Q-Points

- Flat impedance is relative, and difficult to pull off

- Low Q PDN

- Lower reaction to transient changes, minimal ringing present

- Impedance and high Q resonances look similar, but have different causes

- Impedance resonance due to passive resonance of system, present at power on and off

- High Q resonance due to VRM feedback loop, only present with power on

Source: Witcher, S., Sandler, S., DesignCon (2023). A New Power Integrity Requirement to Supplement Target Impedance: Quantifying PDN Impedance Flatness from Sandler NISM Santa Clara, CA; DesignCon.

#DesignCor

JAN. 30 - FEB. 1, 2024

10

(informa markets

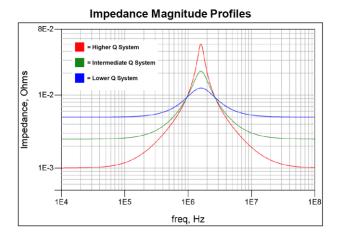

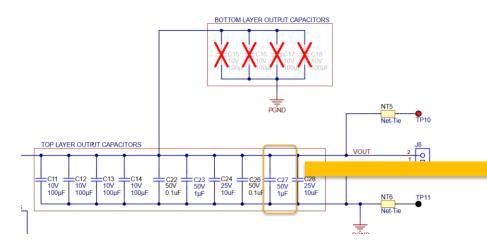

## **Demo 1, TPSM843B22**

#### TPSM843B22 Evaluation Board, TPSM843B22EVM

- $_{\odot}$  VIN: 4V to 18V

- o VOUT: 0.5V to 7V

- o Max Current: 20A

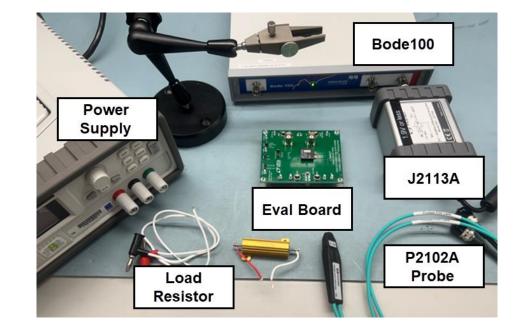

#### Equipment Used

- o Omicron Bode100

- J2113A Semi-Floating Differential Amplifier

- o P2101A 2-Port Probe

- o Keysight N2787A Probe Holder

#DesignCon

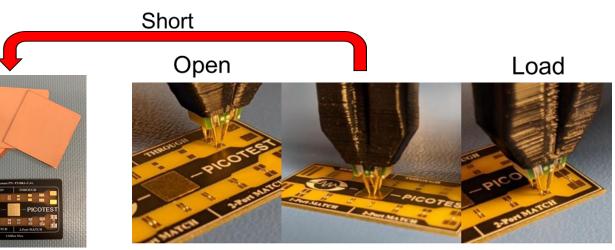

#### **Demo 1, Setup and Calibration**

- The effects of cables, connectors, and probe tips must be zeroedout before measurements can be taken

- A short, open, load (SOL) calibration helps us set the reference point of our measurement to the device under test (DUT)

Picotest P2102A Probe

\*Short calibration with 5oz copper reduces noise floor of measurement setup.

JAN. 30 - FEB. 1, 2024

#DesignCon

12 (informa markets

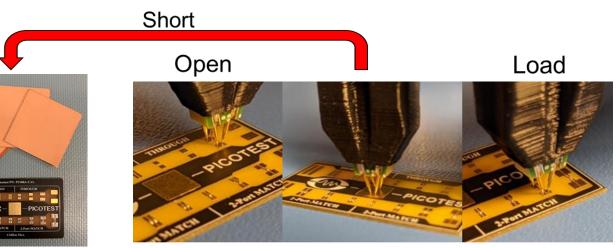

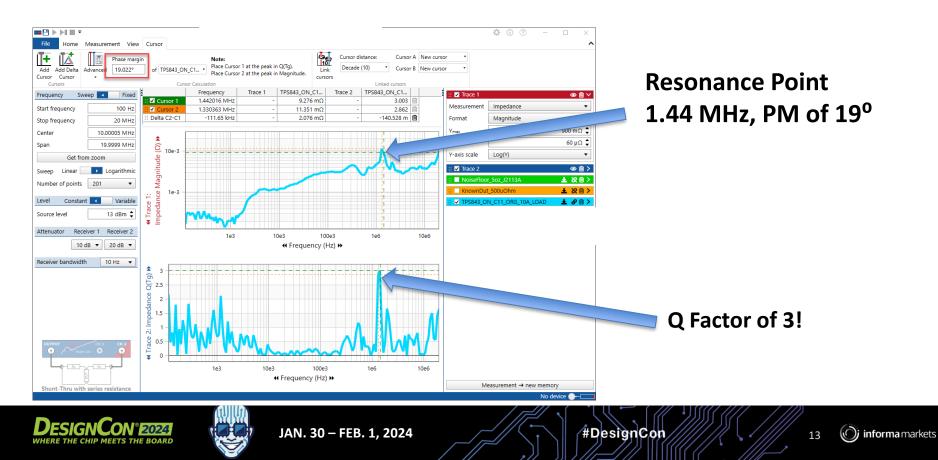

#### **Measurement of Output Impedance (Zo)**

## What can fix this resonance point?

| m1                                   | ] |

|--------------------------------------|---|

| freq=1.316 MHz                       |   |

| mag(TPS843_ON_C11_ORG_10A_LOAD)=0.01 |   |

Step 1: Determine peak inductance (from Z)

$$L_{peak} = \frac{X_L}{2\pi f} = \frac{11m\Omega}{2 \cdot \pi \cdot 1.316 MHz} = 1.33nH$$

Step 2: Determine  $Z_{TGT}$  and solve for C.

$$C = \frac{L_{peak}}{R^2} = \frac{1.33 \ nH}{(8 \ m\Omega)^2} = 21 \ \mu F$$

#DesignCon

Step 3: Find equivalent capacitor, set capacitor ESR  $\leq Z_{TGT}$  and update design

Select -> 22  $\mu$ F capacitor with ESR  $\leq$  8 m $\Omega$

JAN. 30 - FEB. 1, 2024

## Adding a 22 µF Capacitor to the Eval Board

• Swapped a 1uF Capacitor, with a resonance frequency of 10 MHz with a 22uF capacitor, with an ESR of 4 m $\Omega$ , as  $Z_o < Z_{TGT}$  at 10MHz

C27 Original: GCM21BR71H105KA03L C27 New: 885012107011

#DesignCon

JAN. 30 - FEB. 1, 2024

#### **Measurement of Zo with Updated Capacitor**

JAN. 30 - FEB. 1, 2024

16

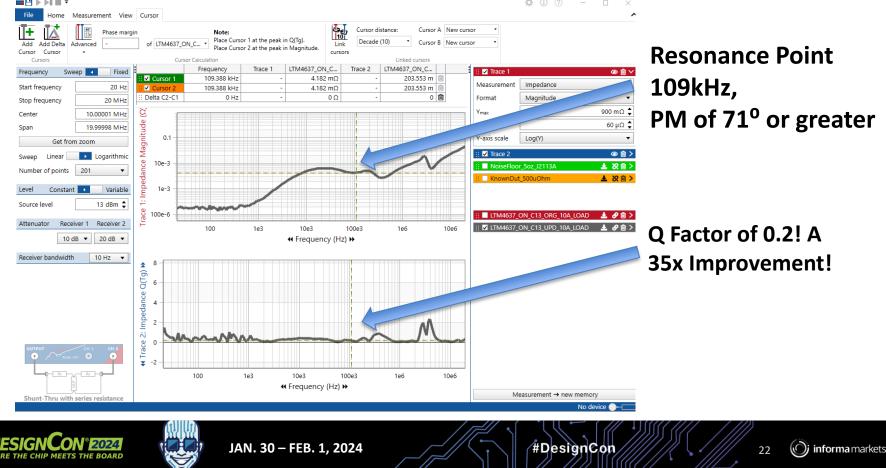

## Demo 2, LTM4637

- LTM4637 Evaluation Board, DC1872A

- $_{\odot}$  VIN: 4.5V to 20V

- o VOUT: 1V to 1.8V

- o Max Current: 20A

#### Equipment Used

- o Omicron Bode100

- J2113A Semi-Floating Differential Amplifier

- o P2101A 2-Port Probe

- o Keysight N2787A Probe Holder

#DesignCon

#### **Demo 2, Setup and Calibration**

- The effects of cables, connectors, and probe tips must be zeroedout before measurements can be taken

- A short, open, load (SOL) calibration helps us set the reference point of our measurement to the device under test (DUT)

Picotest P2102A Probe

\*Short calibration with 5oz copper reduces noise floor of measurement setup.

JAN. 30 - FEB. 1, 2024

#DesignCon

18

(informa markets

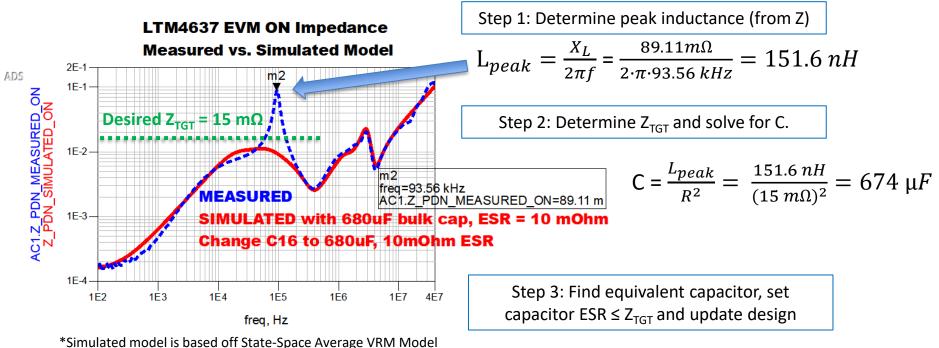

## Demo 2, Meas. of Zo at C13

## What can fix this resonance point?

Select -> 680  $\mu\text{F}$  capacitor with ESR  $\leq$  15 m $\Omega$

#DesignCon

JAN. 30 - FEB. 1, 2024

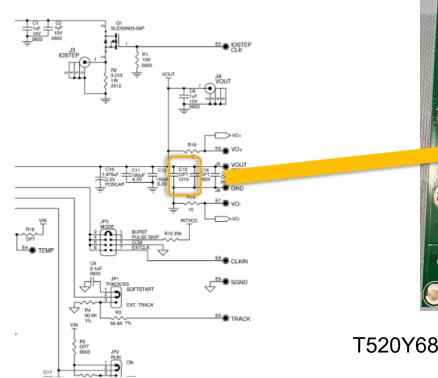

#### Adding a 680 µF Capacitor to the Eval Board

#### T520Y687M004ATE010, 680 $\mu\text{F},$ 10 m $\Omega$ ESR

#DesignCon

JAN. 30 - FEB. 1, 2024

## Measurement of Zo with Updated Capacitor

#### **Call to Action**

- Do not trust vendor reference designs, they are not always correct

- Just because these VRMs are not stable does not mean they are bad. It means they

are not integrated with PDN correctly.

- The PDN for a VRM design needs to be optimized for each application.

- By using NISM, a designer can measure the output impedance see the output impedance, and quickly determine PDN stability

#### Conclusion

- Both demonstrations showed that bill of material (BOM) changes had a dramatic impact on system stability. Additional BOM changes could further improve stability across entire system

- Accurate calibration and low inductance measurement paths are a must to properly measure impedance in the system PDN

- NISM is simple, accurate and widely available. Designing NISM test points is significantly easier than Bode Plot test points, and NISM can be implemented as part of final design and system sign-off

- Power integrity includes everything from the power supply to the load. This entire system needs to be included and measured for the system PDN to meet requirements. PDN design is specific to each application!

#DesignCor

JAN. 30 - FEB. 1, 2024

#### References

[1] Barnes, H. (2021). Power Integrity Target Impedance Says it All, Power Delivery is AC not DC. *14th Annual Central PA Center for Signal Integrity Symposium*, (pp. 1-54). Harrisburg.

[2] Sandler, S. (2019). Why Full VRM Characterization is Essential. Signal Integrity Journal

[3] Witcher, S., Sandler, S., DesignCon (2023). A New Power Integrity Requirement to Supplement Target Impedance: Quantifying PDN Impedance Flatness from Sandler NISM Santa Clara, CA; DesignCon.

[4] Sandler, S., Barnes, H., Dannan, B., (2023). *CHIPHEADS, Hands-On PDN Impedance and Calibration Basics;* Santa Clara, CA; DesignCon

[5] What is Non-Invasive Stability Measurement (NISM)- https://www.picotest.com/non-invasive-stability-measurement.html

# Thank you!

#### **QUESTIONS?**

JAN. 30 - FEB. 1, 2024

#DesignCon