# Improved Methodology to Accurately perform System Level Power Integrity Analysis Including an ASIC die

Benjamin Dannan, Northrop Grumman James Kuszewski, Northrop Grumman Will McCaffrey, Northrop Grumman

Benjamin Dannan (Northrop Grumman), James Kuszewski (Northrop Grumman), Ramzi Vincent (Northrop Grumman), Shin Wu (Northrop Grumman), Will McCaffrey (Northrop Grumman), Albert Park (Northrop Grumman)

APRIL 5 – 7, 2022

#DesignCon

### **SPEAKERS**

#### **Benjamin Dannan**

Technical Fellow & Staff Dig Eng, Northrop Grumman

benjamin.dannan@ngc.com | northropgrumman.com

Benjamin Dannan is a Technical Fellow and a Staff Digital Engineer at Northrop Grumman Mission Systems. He has a BSEE from Purdue University, a Masters of Engineering in Electrical Engineering from The Pennsylvania State University, and graduated from the USAF Undergraduate Combat Systems Officer training school with an aeronautical rating. He received the prestigious DesignCon best paper award in 2020 and is also a Keysight Certified Expert in ADS.

#DesignCon

Approved for Public Release: Distribution is Unlimited: #22-0319: Dated 03/08/22

#### Will McCaffrey

Principal Digital Engineer, Northrop Grumman

william.mccaffrey@ngc.com | northropgrumman.com

Will McCaffrey is a Principal Digital Hardware Engineer at Northrop Grumman Mission Systems. He holds a BSEE from Rochester Institute of Technology in Rochester NY, and currently pursuing a MSEE at Johns Hopkins University. Since 2018 he has designed hardware interconnects for a CubeSat, designed several DDR4 implementations on high speed mixed-signal PCBs as well as designed his own highspeed mixed signal PCB. His interest is in high-speed digital design and SI/PI simulations

#### James Kuszewski

Technical Fellow & Consulting Dig Eng, Northrop Grumman

james.kuszewski@ngc.com | northropgrumman.com

Jim Kuszewski is a Technical Fellow and a Consulting engineer at Northrop Grumman Mission Systems. He holds a BSEE from Michigan State University and a MSCS from the Johns Hopkins University. Jim is the founder of the Northrop Grumman Mission Systems Signal Integrity / Power Integrity Community of Practice. He has also worked on design automation, system security and product integrity initiatives. Currently Jim oversees many programs which use high density, multi-gigabit speed SerDes, DDR memory, mixed signal, fine pitch, and high-power dissipation digital components as well as multi-chip module substrate design.

## **Today's Key Takeaways**

- Know what your target PDN impedance needs to be for your VRM, board, substrate and die.

- A clear methodology on how to know if the voltage ripple at the die bumps on a substrate is within the defined specification of the ASIC

### **Overview**

- Power integrity challenges and drivers with ASICs

- PI Methodology workflow with ASICs

- CPM model generation

- Calculating your target impedance

- Substrate model generation and optimization

- Full PDN analysis

- CPM modulation

- Time domain analysis with voltage ripple

- Next steps

- Summary

- Questions

#DesignCor

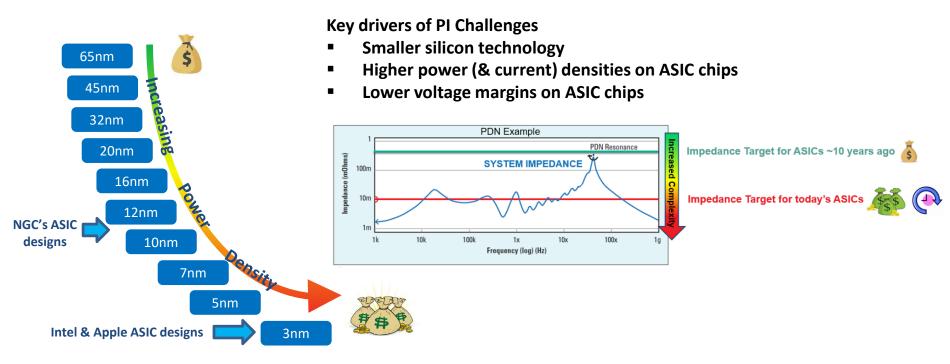

# **Power Integrity Challenges and Drivers**

Impedance design targets for today's ASICs cost more money & time to develop

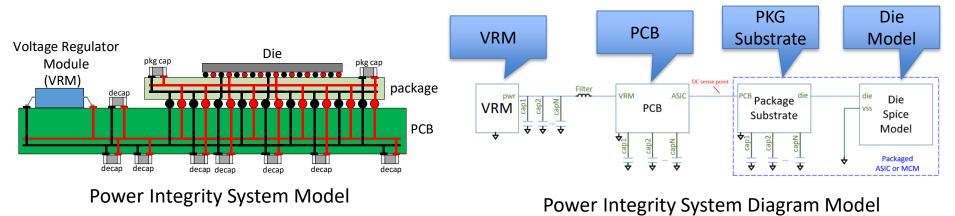

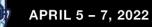

### **Definition of PI Workflow with ASICs**

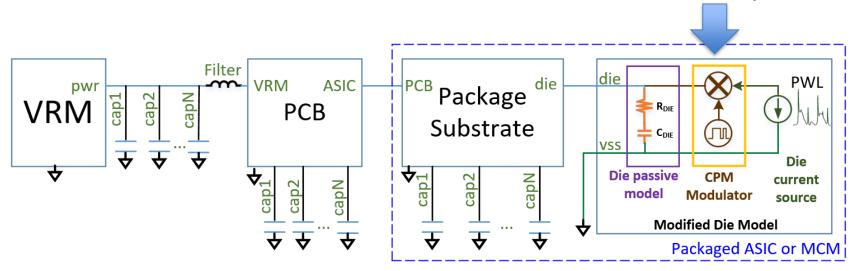

4 Main Blocks for PI System Analysis

As node geometries decrease on ASICs, there are more transistors causing additional current draw and voltage ripple requirements are tighter.

#### We cannot change the current draw, but we can manage the voltage ripple

#DesignCon

Approved for Public Release; Distribution is Unlimited; #22-0319; Dated 03/08/22

## **Definition of PI Workflow with ASICs**

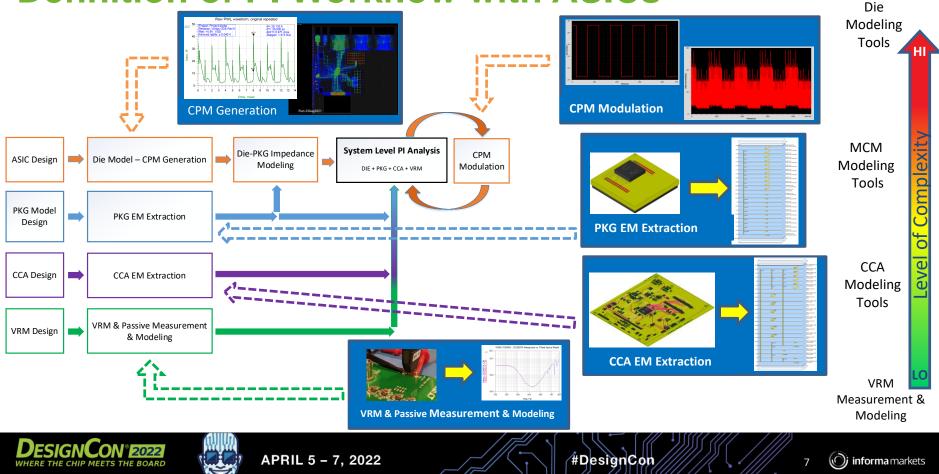

### **Die Model Extraction - Partial versus Looped Model**

#### Partial die Model

Looped die Model

die Spice Node 0 enabled with die model

- By disabling spice node 0, VDD and VSS are referenced to each other which is essential for the current loop when generating the CPM model

- For looped models, the passive elements on the VDD rail is the combination of passive elements of the actual VDD and actual VSS rails

#DesignCon

() informa markets

8

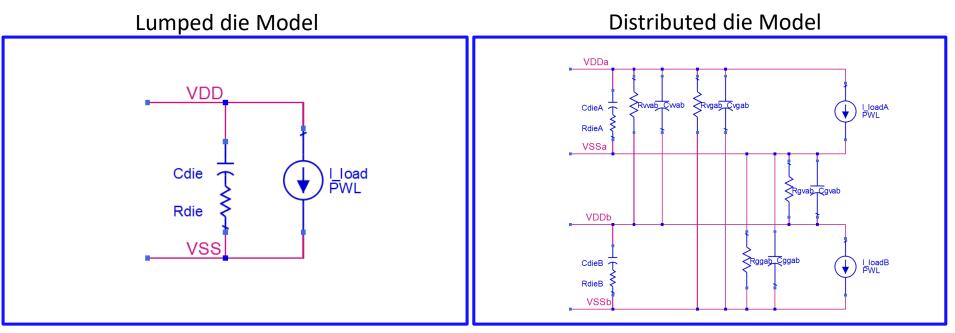

#### **Die Model Extraction - Lumped versus Distributed Model**

- Lumped models have one load current, one C<sub>DIE</sub>R<sub>DIE</sub> and two nodes

- Distributed models have multiple load currents, with multiple C<sub>DIE</sub>R<sub>DIE</sub>, one node per die bump, and passive interaction between all nodes

#DesignCon

() informa markets

Approved for Public Release; Distribution is Unlimited; #22-0319; Dated 03/08/22

#### **Die Model Extraction Comparison Verification**

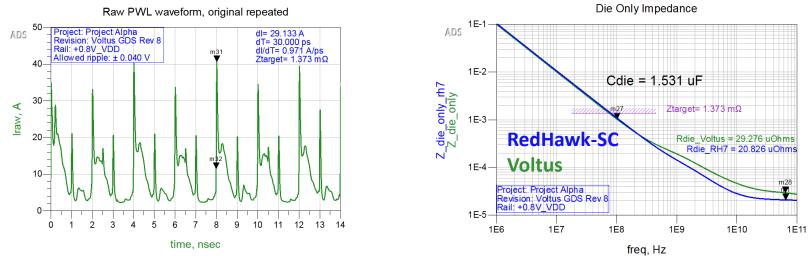

- The CPM Die model Extractions consists of 2 primary components:

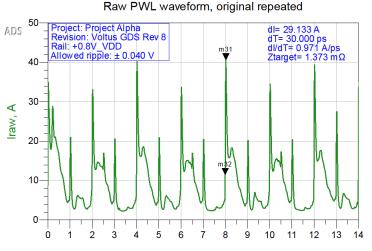

- 1. Piece-wise linear (PWL) waveform representing current at the die bumps

- 2. Passive spice model which includes  $R_{DIE}$  and  $C_{DIE}$

\*Recommendation is to generate CPMs as lumped and looped model

Extracted die model shows great correlation with 2 EDA tools, which also validates our passive die model!

### **Target Impedance – The Traditional Way**

- Typically, the expectation is to calculate Z<sub>TARGET</sub> based on the maximum transient current.

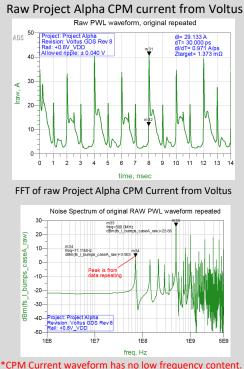

- Using the PWL waveform example shown

$Z_{TARGET} = \frac{\Delta V}{\Delta I}$

- $\Delta V$  is the allowed voltage variation  $\Delta I$  is the current change where dI/dT is maximum  $\Delta V = V_{RIPPLE} = 5\%$  of 0.8V = 40mV,  $\Delta I = 29.133A$

- This makes  $Z_{TARGET} = 1.37 m\Omega$

- Analysis shows that violation of this impedance target will still provide a V<sub>RIPPLE</sub> in spec. Therefore, this Z<sub>TARGET</sub> is too conservative!

#DesignCor

time, nsec

informa markets

11

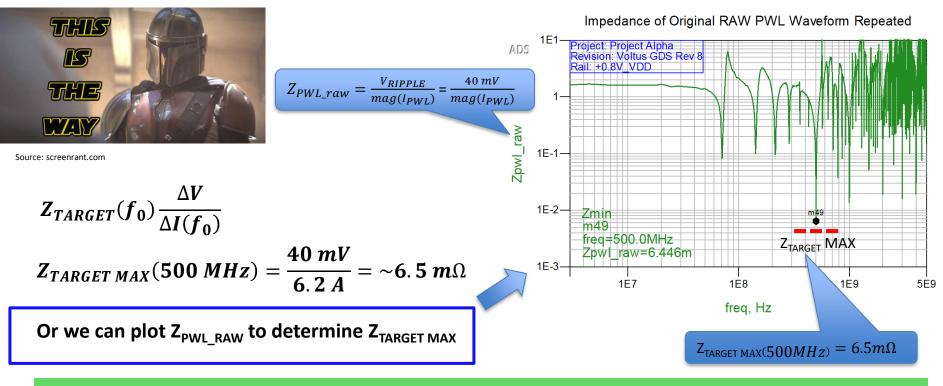

### **Target Impedance – The Right Way with a CPM**

Z<sub>PWL RAW</sub> Lowest impedance point can be used to calculate Z<sub>TARGET</sub> for entire PDN for this CPM's PWL waveform

#DesignCon

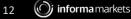

#### **Noise Spectrum of CPM**

- CPM generation is very compute intensive

- Modeled dynamic current only represents a short window of actual die activity (typically a few clock cycles)

- When repeating the CPM data, artifacts are created in the noise spectrum.

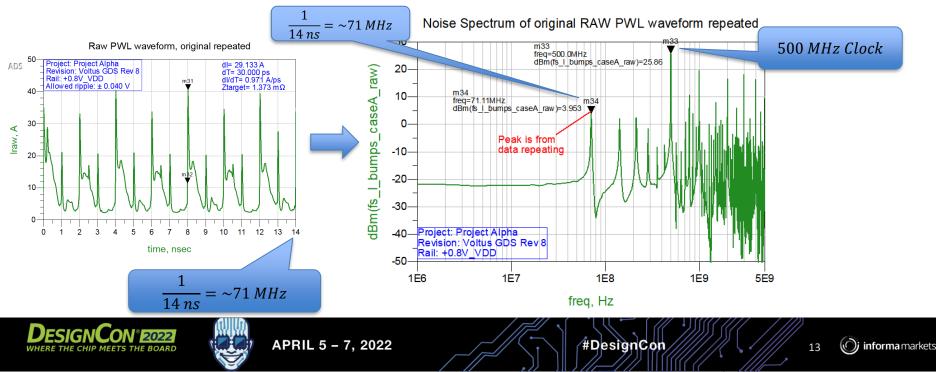

### **Die Model Analysis - Calculating C<sub>DIE</sub> and R<sub>DIE</sub>**

#DesignCon

APRIL 5 – 7, 2022

14 (

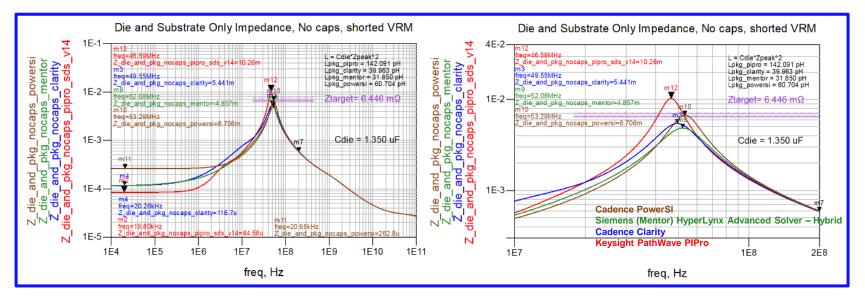

#### **Substrate Artwork Extraction Verification**

#### Setup for Model Shown

#### Correlation shown across multiple EM tools, this validates substrate artwork extraction

### **Substrate Design Goals**

Calculating max L<sub>PKG</sub> (L<sub>PKG IDEAL</sub>) to meet design goal of Z<sub>TARGET</sub>

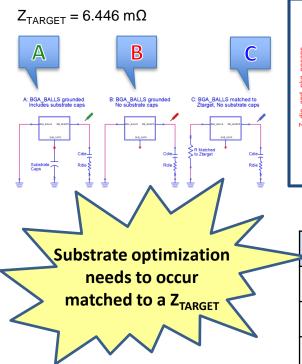

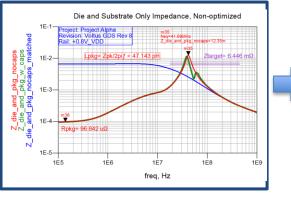

$Z_{\text{TARGET}} = 6.446 \text{ m}\Omega$

$L_{PKG \, IDEAL} = \frac{Z_{TARGET}}{2\pi f} = \frac{6.446 \, m\Omega}{(2\pi)(100 MHz)} = 10.3 \, pH$

However, (L<sub>PKG IDEAL</sub>) represents a very low inductance that would require an excessively high number of substrate balls (both die bumps and BGA balls) to meet this inductance.

#### Next step is to consider adding mid-to-high frequency decoupling on-substrate

### **Substrate Artwork Analysis**

After substrate artwork extraction

| $\left  \right $ | PDN Configuration                                                                                             | Impedance Peak (mΩ) | Percent Impedance Change<br>from configuration B |

|------------------|---------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------|

|                  | <b>B</b> : BGA balls grounded, no caps included on the substrate                                              | 12.35               | -                                                |

|                  | A: BGA balls grounded, 43 0.01uF caps included on the substrate                                               | 11.49               | -6.9%                                            |

|                  | <b>C</b> : BGA balls connected to a resistor matching $Z_{\text{TARGET}}$ , no caps included on the substrate | 6.685               | -46%                                             |

#DesignCon

17

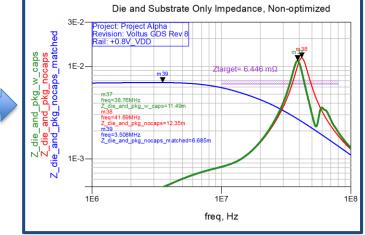

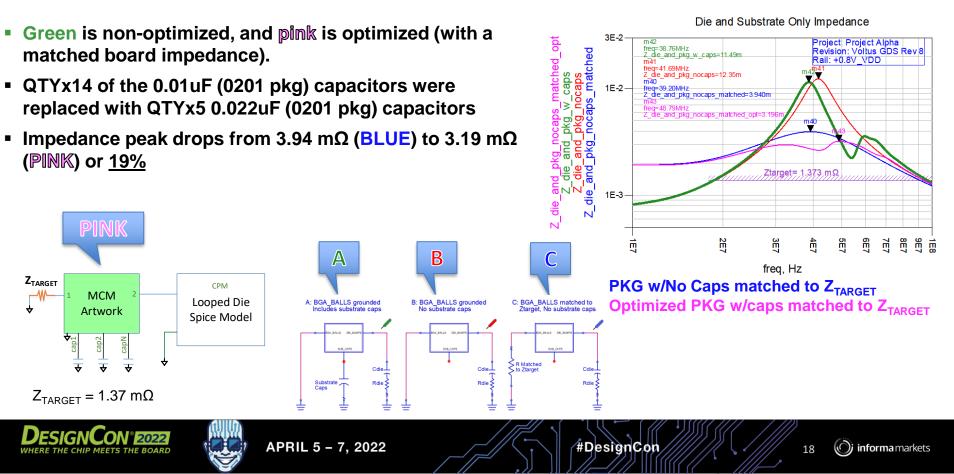

# Package Design Optimization

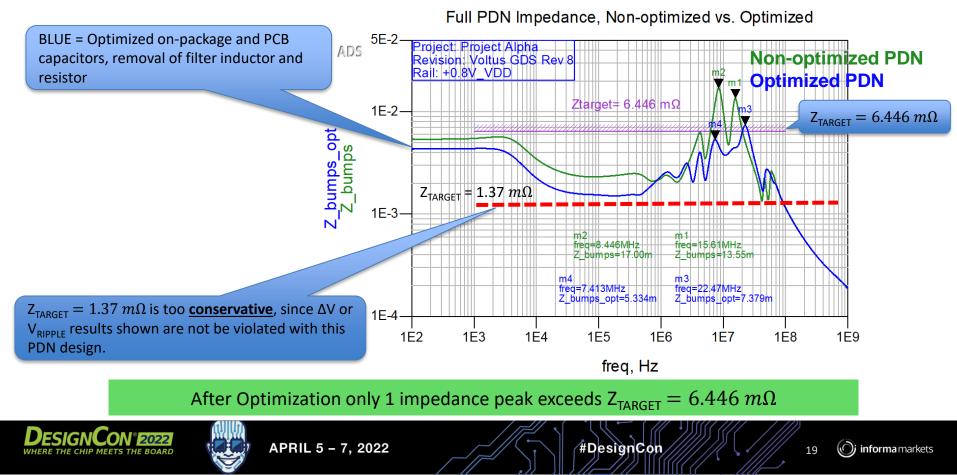

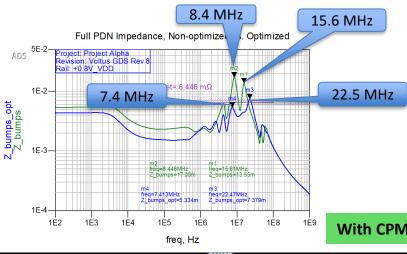

#### **Full PDN Analysis – Impedance**

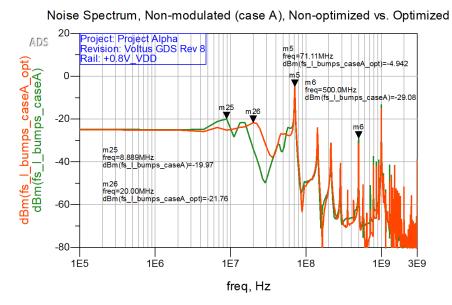

### **Full PDN Analysis – Noise Spectrum**

- Capacitor changes had no effect above ~65 MHz

- At 9 MHz, noise was reduced by 2.5 dBm

- Noise is directly comparable to the impedance profile in the PDN.

Non-optimized PDN – No Modulation Optimized PDN – No Modulation

#DesignCon

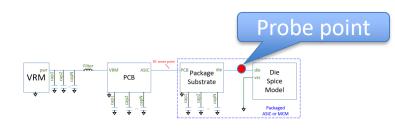

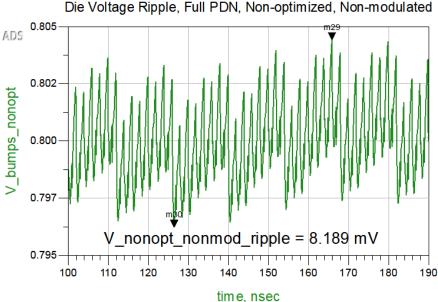

# **Time Domain Voltage Ripple without Modulation**

- ASIC designs expect the IR drop from the bumps to the transistors not to exceed 7.5% of the onchip voltage ripple threshold

- Time domain ripple without modulation on the **Non-Optimized PDN shows**

$\circ \Delta V = 8.189 \text{ mV pk-pk}$

Lower voltage ripple at ASIC die bumps provides more margin within the die design

#DesignCor

21

(informa markets

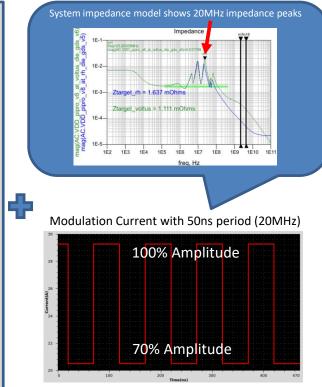

### **CPM Modulation**

CPM Modulator added to PI System Model

CPM Modulation provides a way to create the *Forced Response* on the System

With modulation, it is possible to check for *Rouge Wave* conditions on the system PDN

### **CPM Modulation – Generating the Forced Response**

Entire frequency range of PDN is not covered by raw CPM current

\*Duty cycle =100% current for 25ns and 70% current for 25ns

#DesignCon

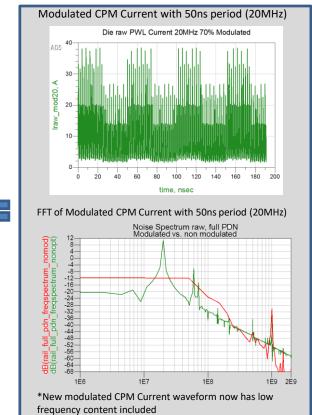

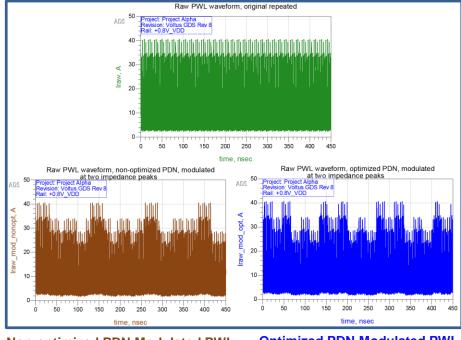

### **CPM Modulation Waveforms**

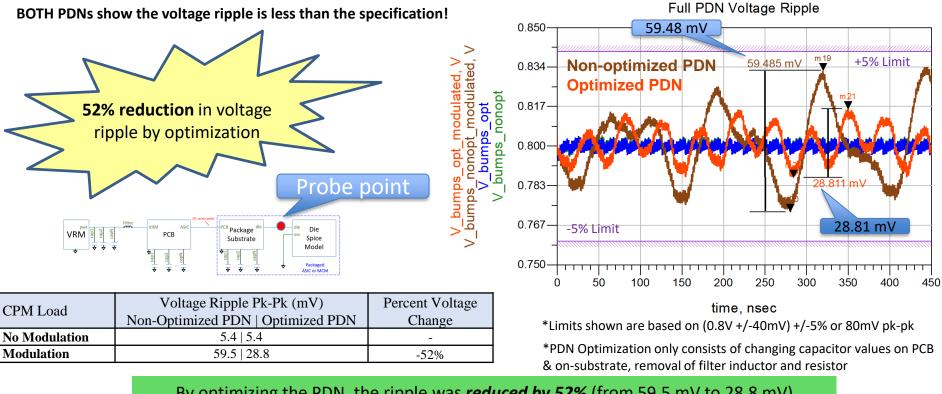

- Based on Non-optimized and optimized PDN, waveforms shown reflect simultaneous modulation at 2 impedance peaks.

- <u>Non-Optimized PDN modulation</u> frequencies 15.6 MHz and 8.4 MHz

- Optimized PDN modulation frequencies 22.5 MHz and 7.4 MHz

Non-optimized PDN Modulated PWL

**Optimized PDN Modulated PWL**

With CPM modulation, it is possible to stimulate the PDN at more than 1 frequency

#DesignCon

24 🦉

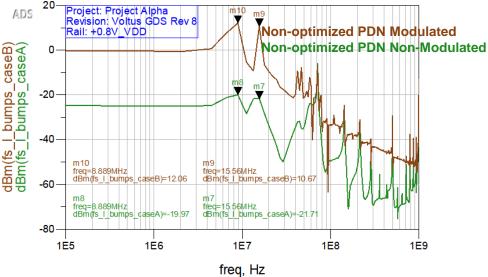

#### Approved for Public Release: Distribution is Unlimited: #22-0319: Dated 03/08/22 Noise Spectrum – Non-Optimized System PDN, Non-Modulated vs. Modulated

- As shown on the Non-optimized PDN, with modulation a difference of

- +32 dBm @ 8.8 MHz vs. without modulation

- +31 dBm @ 15.5 MHz vs. without modulation

- Without modulation, it is not obvious if there is an impact on the PDN changes implemented

Noise Spectrum, Non-optimized, Non-modulated (case A) vs. Modulated (case B)

#### Modulation of the Non-optimized PDN shows an increase of noise by 32 dBm

#DesignCon

(informa markets 25

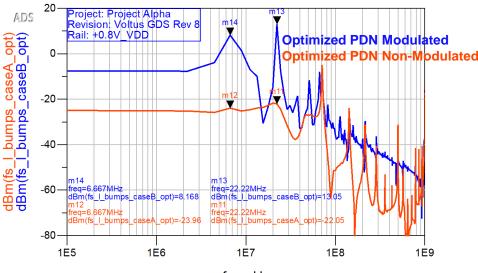

#### Noise Spectrum CPM Modulation vs. Non-Modulation

- As shown on the optimized PDN, with modulation a difference of:

- <u>+32 dBm</u> @ 6.6 MHz vs. without modulation

- +35 dBm @ 22.2 MHz vs. without modulation

- Without modulation, it is not obvious if there is an impact on the PDN changes implemented

Noise Spectrum, Optimized, Non-modulated (case A) vs. Modulated (case B)

freq, Hz

#### Modulation of the Optimized PDN shows an increase of noise by 35 dBm

APRIL 5 - 7, 2022

#DesignCon

26

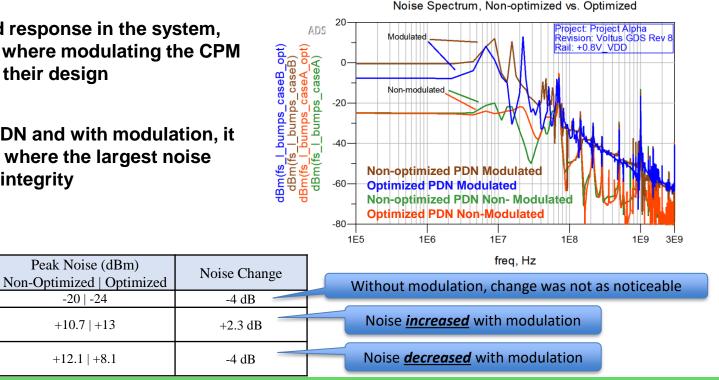

#### Noise Spectrum – Optimized System PDN, Non-Modulated vs. Modulated

- By creating the forced response in the system, this shows designers where modulating the CPM has a large impact on their design

- After optimizing the PDN and with modulation, it is easier to determine where the largest noise sources are to power integrity

By optimizing the PDN, the noise *increased by 2.3 dB and reduced by 4 dB* at the modulation peaks in comparison to the non-optimized PDN, but overall noise is reduced

**PDN** Configuration

84% Modulation at first

84% Modulation at second

No Modulation

impedance peak

impedance peak

APRIL 5 – 7, 2022

$-20 \mid -24$

+10.7 | +13

+12.1 | +8.1

#DesignCon

27

(informa markets

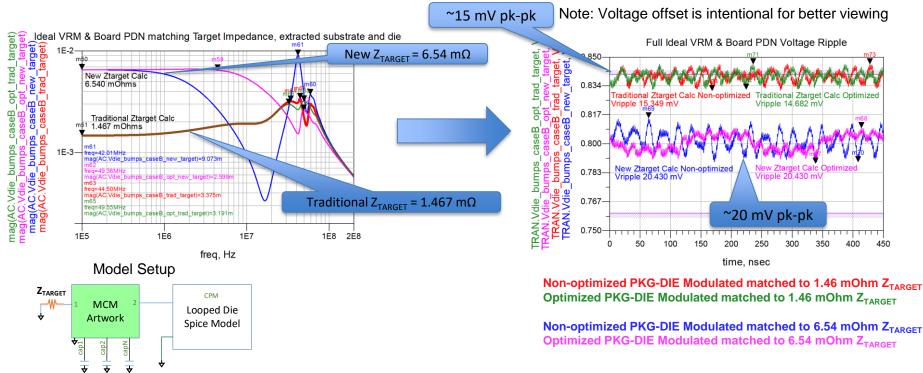

#### Matching Target Impedance and PDN Voltage Ripple

#### The closer the PDN is to matching $Z_{TARGET}$ , the lower overall voltage noise response

APRIL 5 – 7, 2022

#DesignCon

28

informa markets

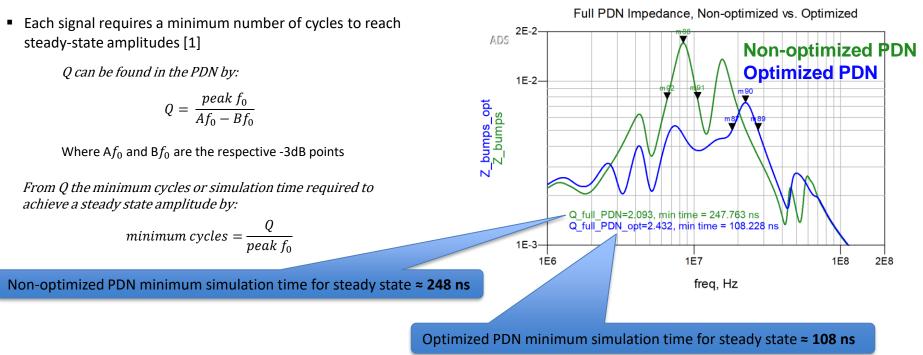

#### **Determining Simulation Duration for Steady State Amplitude**

#### For the forced response to work, the simulation needs a minimum number of cycle to charge the PDN [1]

APRIL 5 – 7, 2022

29 (informa markets

### Full PDN Analysis – Time Domain Voltage Ripple

By optimizing the PDN, the ripple was reduced by 52% (from 59.5 mV to 28.8 mV)

#DesignCon

30

Approved for Public Release; Distribution is Unlimited; #22-0319; Dated 03/08/22

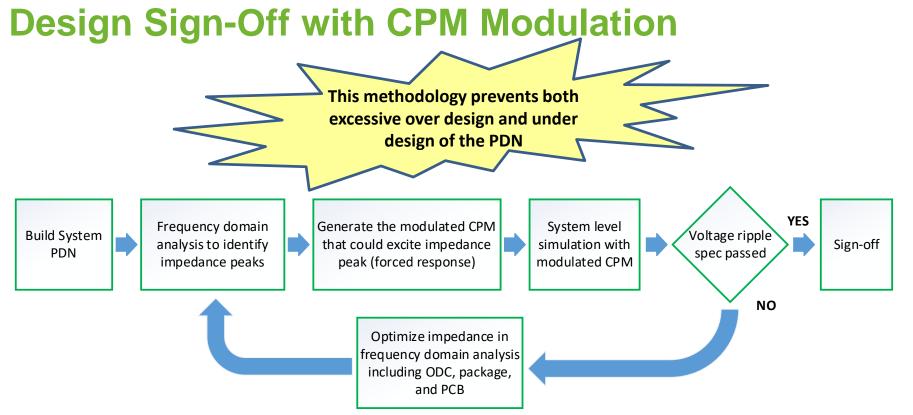

Initial analysis occurs in the frequency domain with PDN design  $\rightarrow \underline{Design \ sign-off} \ occurs \ in the \underline{time \ domain!}$

informa markets

#### Approved for Public Release; Distribution is Unlimited; #22-0319; Dated 03/08/22

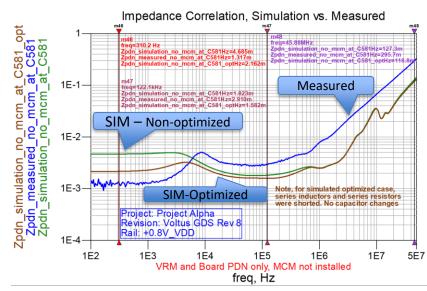

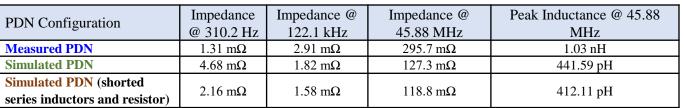

#### **PDN Measurement of PCB**

Room for improvement in measurement correlation could be addressed by:

- To more accurately depict the inductor DCR

- VRM model improvement

- Vendor capacitor model improvement

- PCB measurement indicates extractions are less resistive

#DesignCon

2 (1

\*Rs =  $0\Omega$  on P2102A-1X Probe

**Measurement Setup**

CH 2

•

0

Common Mode

Choke or Isolator

Bode 100

Source: Picotest.com

## **Next Steps**

Next steps include:

- Analysis of PDN with capacitor models that have mounting inductance removed to achieve better measurement correlation.

- Analysis using VRM state space average models

- Measurements in the time domain to validate the CPM models

In this example, the measured capacitor has the same impedance as the vendor model at nearly 10x the frequency

#DesignCon

Source: EDICon 2021 Partial Inductance – The secret to correlating simulation and measurement – S. Sandler, B. Dannan, & H. Barnes

33

# **Summary**

- Demonstrated PI methodology with ASICs to achieve higher fidelity simulation using CPMs

- Discussed the importance of CPM modulation to generate a forced response as well as use to check for rogue wave conditions

- Showed how design sign-off can occur in time domain, after initial analysis in the frequency domain

- Discussed how target impedance analysis can be used with this method but does not correlate 100% to time domain simulation.

#### For Power Integrity Designs with ASICs....

Source: youtube.com

#DesignCo

34 (O) informa markets

# Thank you!

#### **QUESTIONS?**

Source: dilbert.com

#DesignCon

35

#### References

- 1. Sandler, S., "Target Impedance Limitations and Rogue Wave Assessments on PDN" DesignCon 2015.

- 2. Sandler, S., Dannan, B., and Barnes, H., "Partial Inductance The Secret to Correlating Simulation and Measurement". EDICon 2021.

#DesignCor