## Welcome to DESIGNCON® 2024 WHERE THE CHIP MEETS THE BOARD

Conference

January 30 – February 1, 2024

Santa Clara Convention Center

Expo

January 31 – February 1, 2024

JAN. 30 – FEB. 1, 2024

#DesignCon

# Design, Simulation, and Validation Challenges of a Scalable 2000 Amp **Core Power Rail**

Steve Sandler, Picotest.com Benjamin Dannan, Signal Edge Solutions Heidi Barnes, Keysight Technologies Idan Ben Ezra, Broadcom Semiconductors Yu Ni, Monolithic Power Systems

JAN. 30 - FEB. 1, 2024

#DesignCor

### **Speakers**

#### **Steve Sandler**

Managing Director, Picotest

Steve@Picotest.com | Picotest.com Steve Sandler has been involved with power system engineering for more than 40 years. The founder and CEO of <u>Picotest.com</u>, a company specializing in instruments and accessories for high-performance power system and distributed system testing DesignCon 2023 Engineer of the Year.

#### Heidi Barnes

Power Integrity Applications, Keysight Technologies

<u>Heidi\_barnes@keysight.com</u> | Keysight.com Senior Application Engineer in the PSS EDA Group of Keysight Technologies. Her recent activities include the application of electromagnetic, transient, and channel simulators to solve signal and power integrity challenges. Author of over 20 papers on SI and PI and recipient of the DesignCon 2017 Engineer of the Year.

#### **Benjamin Dannan**

Chief Technologist, Signal Edge Solutions

Ben@signaledgesolutions.com | Signal Edge Solutions Benjamin Dannan is the Chief Technologist at Signal Edge Solutions, a senior member of IEEE, and an experienced signal and power integrity (SI/PI) design consultant, advancing high-performance ASICs and developing advanced packaging solutions for high-speed digital designs.

#### Idan Ben Ezra

HW and PI Engineer, Broadcom Ltd

#### Idan.benezra@Broadcom.com | Broadcom.com

Hardware and PI engineer at Broadcom Semiconductors, DNX group of CSG-Switch Products, in Israel. In Broadcom Idan is a Focal point in full system Power Delivery Network analysis design stages. Idan has hands-on experience with lab power measurements including correlation to simulation.

JAN. 30 - FEB. 1, 2024

#DesignCon

(i) informa markets

### Outline

- Who and Why needs 2000 Amps?

- How do we build it?

- Validation with Step Loader How Hard is This?

- Measure-Based Modeling of the Components and PCB EM Models Why Measure?

- End-to-end Digital Twin Simulations Why Simulate?

- Measurement Case Study It Works!

### Why 2000 Amps?

- Motivation:

- The goal is to demonstrate how one can effectively validate a 2k Amp core power rail design using a substitute 2000 Amps step load device

- Why:

- While 2000 Amps may seem excessive, the increasing processing power of AI, data centers, and supercomputing has already exceeded this current level (NVIDIA X100 ~1500A)

- Challenges:

- VRM solutions including modeling (measured based)

- Driftnet input stage (48V)

- Thermal design

- Simulations for Transient, Frequency, EM, DC, and Electro-Thermal

- How to validate this kind of step

- Projected dynamic current (ultra high speed testing)

- Bandwidth of the current from the package

- ASIC isn't available

#DesignCor

(i) informa markets

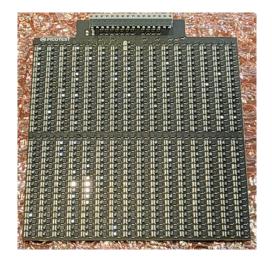

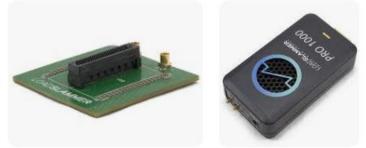

### **Today's 1000 Amp Stepper Solutions**

Renesas 16 power tower solution for 1000A

LoadSlammer for 1000A Peak

### **Next-Generation 2000 Amp Stepper Solutions**

Renesas 16 power tower solution for 1000A

Picotest 2000A interposer

LoadSlammer for 1000A Peak

JAN. 30 – FEB. 1, 2024

#DesignCon

informa markets

### Outline

- Who and Why needs 2000 Amps?

- How do we build it?

- Validation with Step Loader How Hard is This?

- Measure-Based Modeling of the Components and PCB EM Models Why Measure?

- End-to-end Digital Twin Simulations Why Simulate?

- Measurement Case Study It Works!

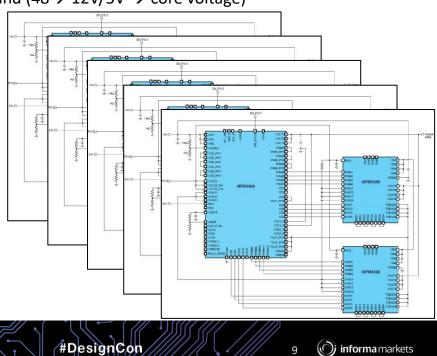

### How to Design a 2000 Amp Power Delivery Solution

- **VRM Vendor**

- MPS and ADI (Analog) only supported this scale

- How:

- Two major architectural paths today (48V  $\rightarrow$  core voltage) and (48 $\rightarrow$  12V/5V  $\rightarrow$  core voltage)

- The implantation:

- 5 x [Controller + 2 Followers] monolithic models (55 phase total)

- Up to 2200A peak and ~2000A SS

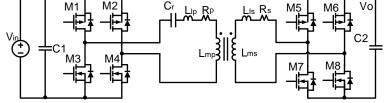

### **Architecture Options to Achieve V<sub>OUT</sub> Core Voltage**

|               | 48V $\rightarrow$ Core Voltage                                                       | $48V \rightarrow 12V/5V \rightarrow Core Voltage$                                                                          |

|---------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Тороlоду      | Resonant Converter                                                                   | Two Stage Buck Converter                                                                                                   |

| Advantages    | <ul><li>Good Efficiency</li><li>Higher Energy Density</li></ul>                      | <ul> <li>Flexible Combinations</li> <li>Multiple Vendors</li> <li>Optimized Cost</li> <li>Wider Operation Range</li> </ul> |

| Disadvantages | <ul><li>Complex Control</li><li>Higher Cost</li><li>Narrow Operation Range</li></ul> | <ul> <li>Lower Energy Density</li> </ul>                                                                                   |

|               |                                                                                      |                                                                                                                            |

JAN. 30 - FEB. 1, 2024

#DesignCon

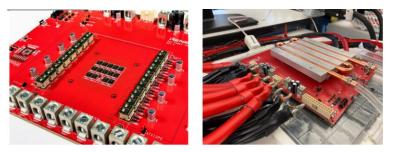

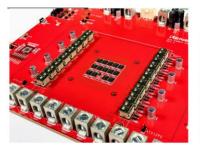

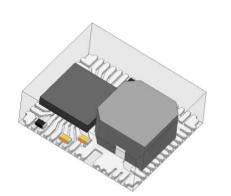

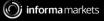

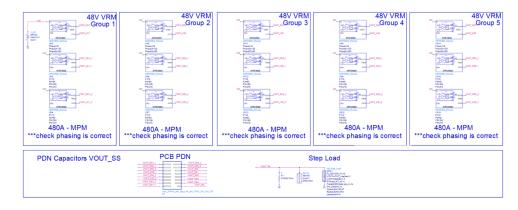

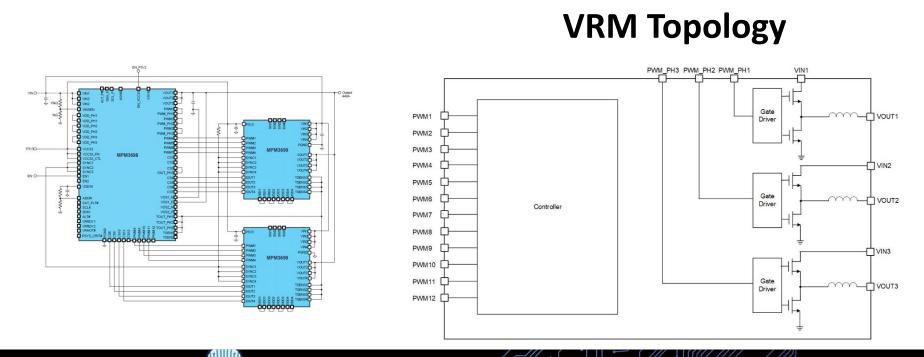

### **Two Stage 2000A Design**

- Fix 4:1 Ratio Step Down 48V -> 12V

- Use Fully Integrated Module 12V -> Core Voltage

- 1 x MPM3698 + 2 x MPM3699 for 400A

- 5 Sets to total 2000A

- Wide V<sub>IN</sub> for 36V to 54V system

- Wide V<sub>OUT</sub> for 0.4V to 3.3V core voltage

#### Scalable Power Delivery Topology 100's of Amps to 1000's of Amps

JAN. 30 - FEB. 1, 2024

MMM

#DesignCon

11 (informa markets

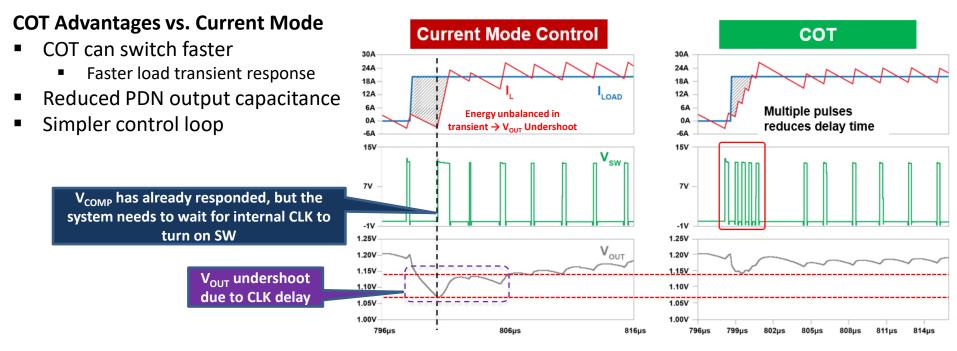

### **Current Mode Control vs. Constant-On-Time (COT) VRMs**

$Source:\ monolithic power.com/en/advantages-of-constant-on-time-control-in-dc-dc-converters$

For same load current step, COT control can switch faster and further reduce V<sub>OUT</sub> undershoot

JAN. 30 - FEB. 1, 2024

#DesignCon

### **Outline**

- Who and Why needs 2000 Amps?

- How do we build it?

- Validation with Step Loader How Hard is This?

- Measure-Based Modeling of the Components and PCB EM Models Why Measure?

- End-to-end Digital Twin Simulations Why Simulate?

- Measurement Case Study It Works!

#DesignCon

### How to Validate PDN with a step loader

- Validation task:

- The validation task involves ensuring that the power delivery network (PDN) can handle such a large load (step and steady state) without causing voltage drops, noise, and other issues that could impact the operation of the system

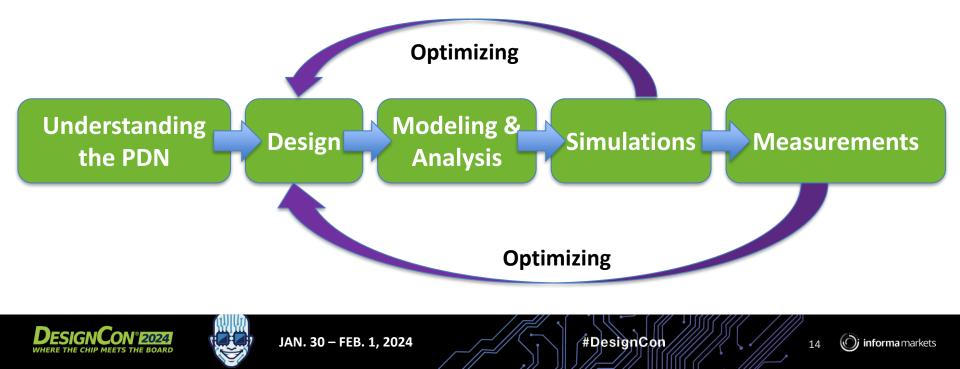

### **PDN Design and Simulation Validating steps**

- Understanding the Power Delivery System

- VRM Vendors, Types, Scales, PDN (PCB, Package and Die)

#DesignCon

### **PDN Design and Simulation Validating steps**

- Voltage Regulation

- Selecting the right multi-phase VRM solution is crucial to achieve a successful working design

- Switching frequency, LBP, TLVR, Load Line, etc.

- Modeling and Analysis

- Using modeling and simulation tools to predict how the load will affect the power delivery system (VRM, PCB, PKG, DIE CPM, Sensing points)

- Simulate the Load The powerful EDA tool

JAN. 30 - FEB. 1, 2024

#DesignCon

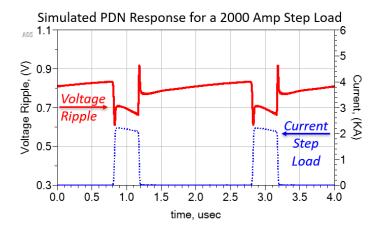

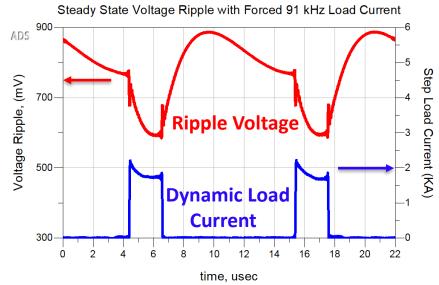

### **Validating PDN Simulation Transient Results**

- Transient Analysis

- This will help to identify the voltage noise ripple magnitude of the undershoot (droop), overshoot (kick), and any

resonant ringing on the power rail

- Noise Analysis

- When adding the Die behavioral di/dt (from the CPM), check for any unwanted noise or spikes in the power rails during the step load transition

#DesignCon

JAN. 30 - FEB. 1, 2024

17 (informa markets

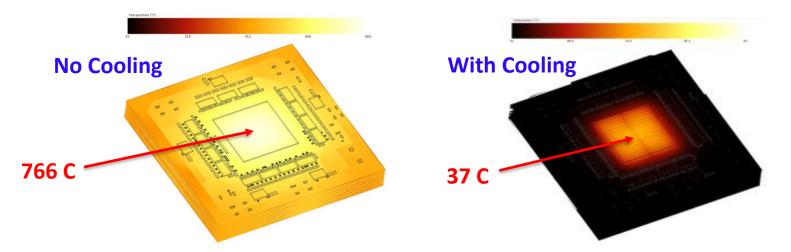

### **Validating Thermal Considerations**

- Thermal Analysis

- Operating at 2000 Amps steady state, along with large dynamic step loads, can generate significant thermal heat rise in components

Thermal analysis for a 2000A load with no cooling on the left, and with cooling on the right. This is a symmetric design, so the hottest location is in the center with 766C on the left with no cooling, and a reasonable 37C on the right with ideal water cooling

JAN. 30 - FEB. 1, 2024

#DesignCon

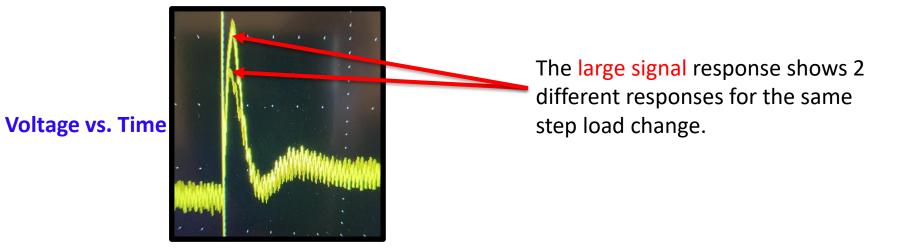

### Large vs. Small Signal Measurement Validation

- Measurement Equipment

- Invest in high-quality measurement equipment before trying to measure this kind of step

- Small signal vs Large signal

- Small signal represent relatively constant signals and typically have small variations around a nominal operating point (DC), how impedance varies with frequency also for stability and noise margins

- Large signal focuses on phenomena such as transient, step response, voltage droop

#DesignCor

JAN. 30 - FEB. 1, 2024

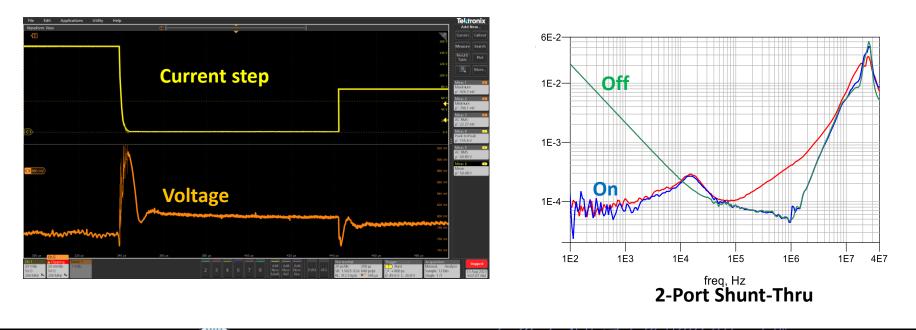

### **Time & Frequency Domain Measurement Validation**

- Testing

- Once we have done the necessary design simulations and know what to expect, it's time to test the system.

- We will check it in both time and frequency domain, voltage drop and Current step

JAN. 30 - FEB. 1, 2024

/////

20

#DesignCor

(informa markets

### **Outline**

- Who and Why needs 2000 Amps?

- How do we build it

- Validation with Step Loader How Hard is This?

- Measure-Based Modeling of the Components and PCB EM Models Why Measure?

- End-to-end Digital Twin Simulations Why Simulate?

- Measurement Case Study It Works!

#DesignCon

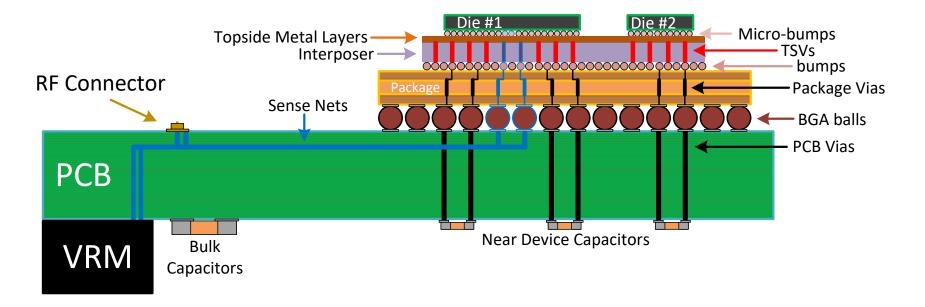

### **Modeling the Source of the Power**

Accurate simulation results require a high-fidelity VRM model and the PCB effects!

JAN. 30 - FEB. 1, 2024

#DesignCon

22

informa markets

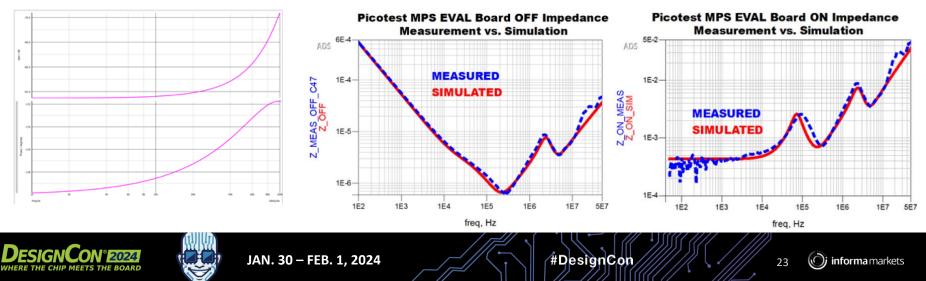

### **Measurement-Based Modeling of the VRM**

- Measurement of VRM impedance (OFF/ON)

- PSRR Model from SIMPLIS used to tune PSRR response of VRM in ADS

- The VRM model was built for MPM3698 since this can be scaled since gain parameters for MPM3698 and MPM3699 were the same

#### Impedance Measurement Setup

#### **PSRR from SIMPLIS**

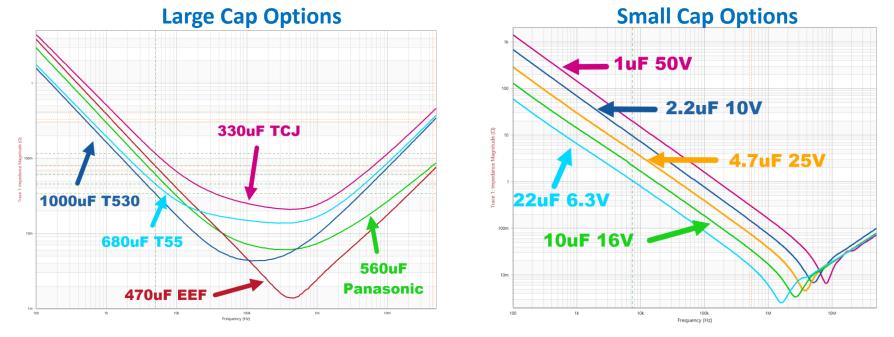

### **Measurement-Based Modeling of the PDN Capacitors**

- There is not an agreed-upon standard Capacitors models from vendors

- Every single capacitor used in this system was measured prior to use in PDN

JAN. 30 - FEB. 1, 2024

#DesignCon

### The Need for PCB EM Models

Power delivery is AC not DC, and no matter how perfect the voltage regulator there is always some parasitic path impedance.

Fast DC IR Drop EM simulations show minor symmetry differences in the PCB power distribution network and optimum placement for sense lines.

#DesignCor

JAN. 30 - FEB. 1, 2024

25

(i) informa markets

### **Digital Twin Accuracy Requires PCB EM Model**

#### Without PCB Effects With PCB Effects 2000 Amp VRM and PDN Impedance 2000 Amp VRM and PDN Impedance Without PCB Effects With PCB Effects 1E ADS ADS 1E-2-1E-2-VRM\_OFF\_Z\_SIM VRM\_ON\_Z\_SIM VRM\_OFF\_Z\_SIM VRM\_ON\_Z\_SIM VRM L = 242.425 pH **VRM OFF** VRM OF 1E-3-1E-3-VRM L = 426.882 pH m2\_91kHz 91kHz m1 VRM ON 1E 1E-4 VRM DCR = 57.441 uOhms VRM ON 1E-5-1E-5-VRM DCR = 2.455 uOhms 1E-6-1E-6-1**F**6 1F7 5E7 1F2 1F3 1F4 1E5 1Ė2 1Ė4 1Ė5 1Ė6 1Ė7 5Ė7 1E3 frea. Hz frea. Hz

22,000% Increase in path resistance! ... And 76% increase in the inductance requires 76% more C!

JAN. 30 - FEB. 1, 2024

#DesignCon

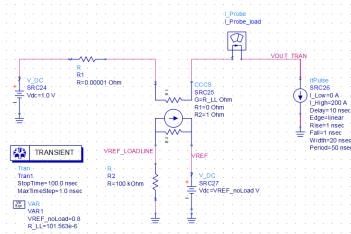

### Modeling of the VRM Load Line Sub-Model

- MPS provides gain parameters of load line within VRM.

- CCCS used to develop Load Line sub-model within VRM

- Load Line delay is adjustable

### $V_{REF \ LOAD \ LINE} = V_{REF} - I_{OUT} \cdot R_{Load \ Line}$

\*Where  $\rm R_{\rm Load\ Line}$  is based off an EQ that is calculated based on register settings of the VRM

JAN. 30 - FEB. 1, 2024

#DesignCon

27 🕥

### **Outline**

- Who and Why needs 2000 Amps?

- How do we build it

- Validation with Step Loader How Hard is This?

- Measure-Based Modeling of the Components and PCB EM Models Why Measure?

- End-to-end Digital Twin Simulations Why Simulate?

- Measurement Case Study It Works!

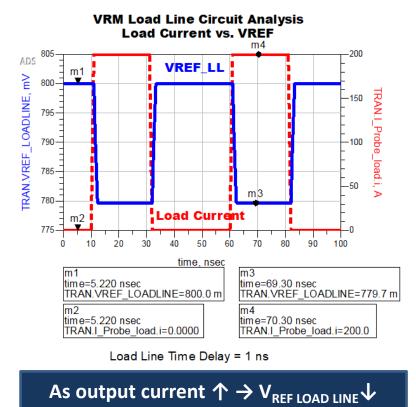

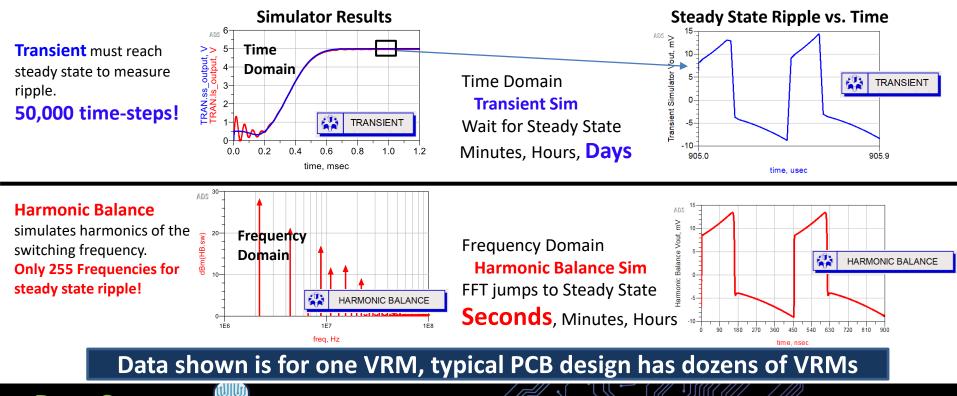

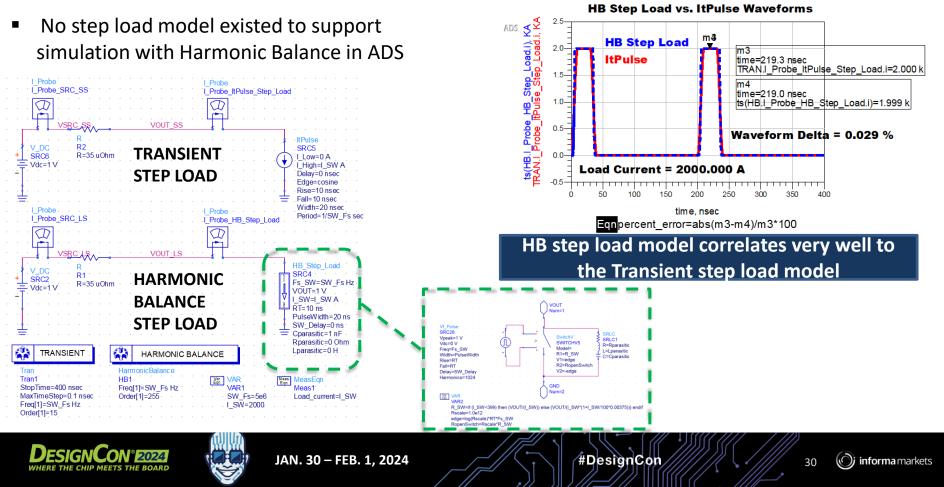

### Why use the Harmonic Balance Simulator with SSAM

Fourier Theory says time domain waveforms are made up of frequency domain waveforms.

JAN. 30 - FEB. 1. 2024

Solving a circuit in the Frequency Domain can be much faster since it limits the frequencies and jumps to steady state.

#DesignCon

Approved for Public Release, NG22-19. © 2022 Northrop Grumman Systems Corporation

(informa markets

### Harmonic Balance Simulation with the Step Load Model

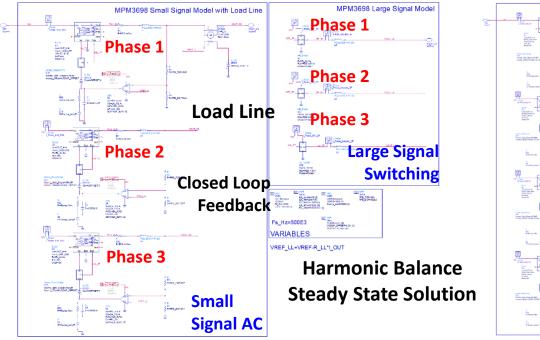

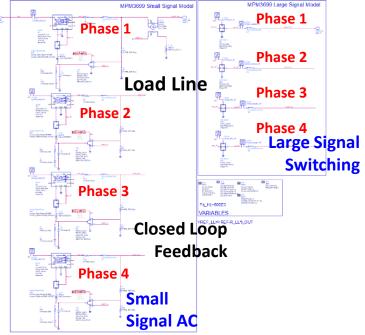

### **Creating the 55-Phase VRM Model with Load Line**

### 5x MPM3698 – 3 phases

### 10x MPM3699 - 4 phases

Sandler State-Space Average VRM Model was used for both the MPM3698 and MPM3699

JAN. 30 - FEB. 1, 2024

· · ////

31

#DesignCon

(informa markets

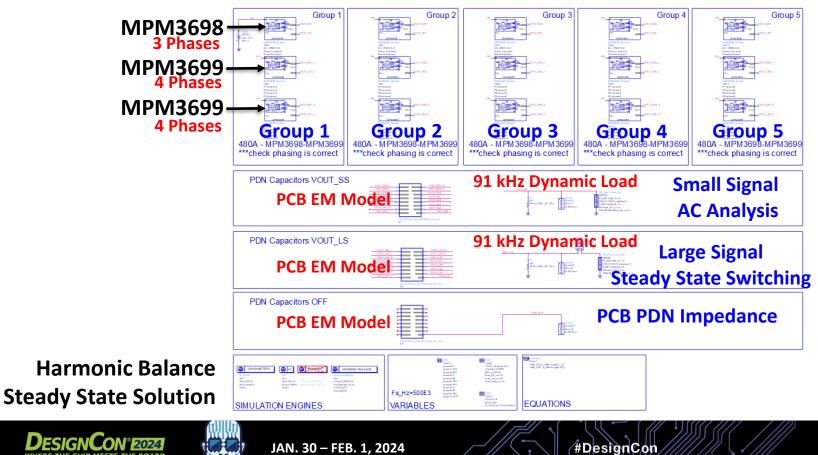

### End-to-End 55 Phase VRM Digital Twin Model

### **End-to-End Digital Twin Simulations**

A complete system simulation model is created with accurate capacitor models, EM-extracted PCB effects, and a 2000A VRM model that was scaled by using 5 groups of MPM3698 and MPM3699 modules

### 55 Phases at 500 kHz Dynamic Load at 91 kHz

Steady State Harmonic Balance Results in 77s

JAN. 30 - FEB. 1, 2024

#DesignCon////

### **Outline**

- Who and Why needs 2000 Amps?

- How do we build it

- Validation with Step Loader How Hard is This?

- Measure-Based Modeling of the Components and PCB EM Models Why Measure?

- End-to-end Digital Twin Simulations Why Simulate?

- Measurement Case Study It Works!

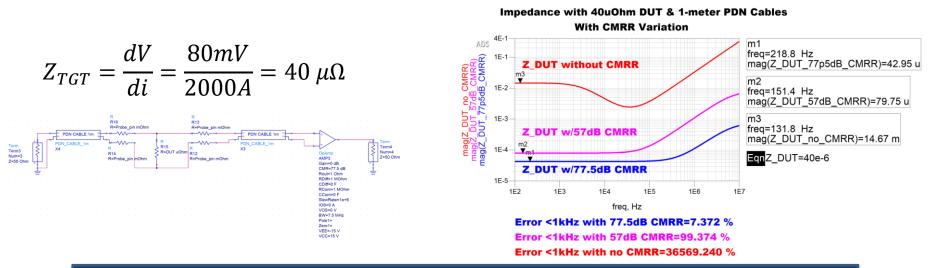

### Measurement Challenges to Measure 40 μΩ PDN With 2-port Probe

- Measuring a 2000 Amp PDN is not intuitive or even a trivial task!

- To measure 2000 A PDN (40 µΩ) a custom injector had to be created

- CMRR, RCABLE, & RPIN are the largest measurement error terms!

Minimum CMRR needed to measure 40  $\mu\Omega$  with 2-port port is 77.5 dB for < 10% error

JAN. 30 - FEB. 1, 2024

#DesignCon

(informa markets

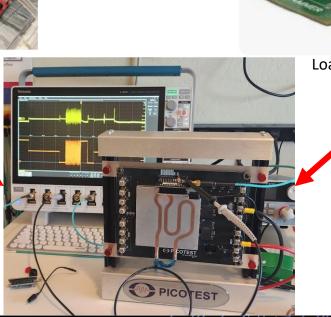

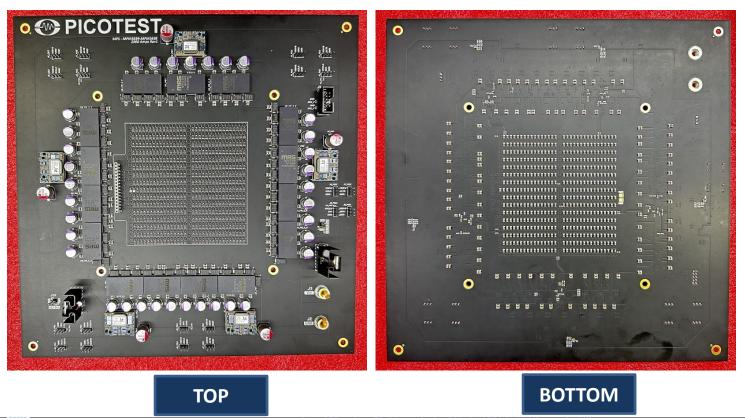

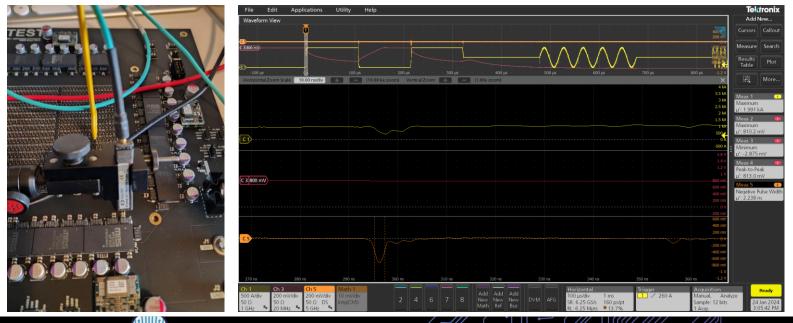

### The 2000 Amp VRM and Step Load Design

- 15 MPS Modules

- 5 Groups

- 5x 48V to 12V

- 512 Load Cells

- 11 bit 50 MS/s

JAN. 30 - FEB. 1, 2024

#DesignCon

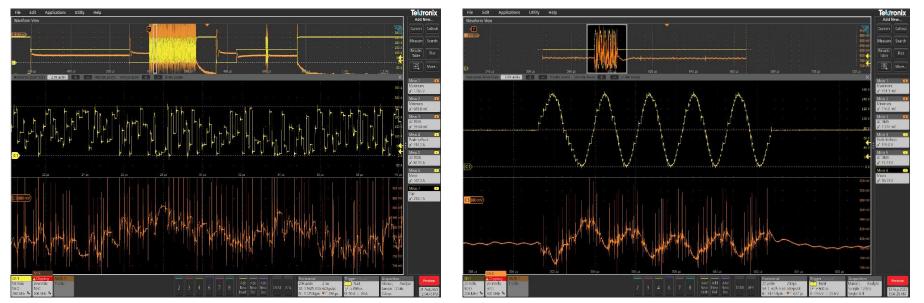

### Measurement Case Study – It Works!

The upper trace shows a demonstration of exponential rise and fall, linear rise and fall, high speed burst, sine and pseudo-random. The zoom window in the lower part of the screen shows the pseudorandom excitation

JAN. 30 - FEB. 1, 2024

#DesignCon///

### Measurement Case Study – It Works!

- Here is a screenshot of one of the decoupling caps using a near field probe.

- Integrating this will provide the current vs time.

- The total time is about 5ns, so the rise time is about 2.5-3ns. This depends mostly on the inductance of the loop through the load switch and decoupling capacitor.

JAN. 30 - FEB. 1, 2024

#DesignCor

## **Conclusion and Summary**

- 2000 Amp delivery is here to stay and even higher!

- Step Loader validation is the only way to get accurate large signal dynamic behavior

- Simulation accuracy requires measurementbased models for VRM SSAM and capacitors; PCB EM models

- Digital twin 55 phases, load-lines, dynamic load HB simulation in minutes

- Hardware measurements prove scalable 2000 Amp step load can be done!

#DesignC

# Thank you!

### **QUESTIONS?**

JAN. 30 - FEB. 1, 2024

#DesignCon

### References

- 1. Advantages of Constant-On-Time Control in DC/DC Converters <u>https://www.monolithicpower.com/en/advantages-of-constant-on-time-control-in-dc-dc-converters</u>

- Dannan, B., & Sandler, S. M. (2023, December). The Challenge of Measuring a 40 μΩ, 2000 Amp PDN With a 2-Port Probe: How Much CMRR is Needed? Extreme Measurement Blog. <u>https://www.signalintegrityjournal.com/</u>

- 3. Dannan, B., & Sandler, S. M. (2024, January). The Challenge of Measuring a 40 μΩ, 2000 Amp PDN With a 2-Port Probe: The Measurement Result. Extreme Measurement Blog. https://www.signalintegrityjournal.com/

- 4. S. Sandler, B. Dannan, H. Barnes, and C. Yots, "VRM Modeling and Stability Analysis for the Power Integrity Engineer", DesignCon 2023.

- 5.

#DesignCon

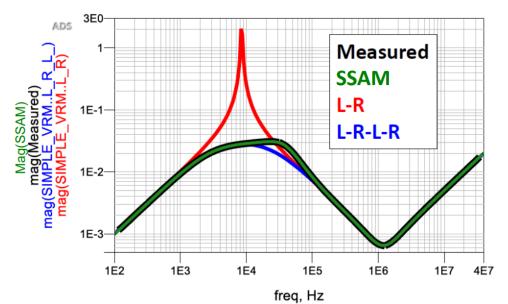

### Modeling the Source of the Power

A poor fidelity State-Space Average Model is significantly better than a good R-L VRM model

Model Comparison

S. Sandler, B. Dannan, H. Barnes, and C. Yots, "VRM Modeling and Stability Analysis for the Power Integrity Engineer", DesignCon 2023.

#DesignCon

JAN. 30 – FEB. 1, 2024

42 (informa markets